Mục lục:

- Bước 1: Thao tác của người dùng với Digital Sequencer

- Bước 2: Chi tiết kỹ thuật

- Bước 3: Chi tiết kỹ thuật

- Bước 4: Bộ chia đồng hồ 7 đoạn

- Bước 5: Nhịp đập mỗi phút đồng hồ chia

- Bước 6: Pitch dải phân cách đồng hồ

- Bước 7: Phát / Tạm dừng / Chọn trạng thái Máy

- Bước 8: Phát / Tạm dừng / Chọn trạng thái máy

- Bước 9: Đầu ra FSM

- Bước 10: Đầu ra FSM

- Bước 11: Gán ghi chú

- Bước 12: Chọn đầu ra

- Bước 13: Thế hệ sóng vuông

- Bước 14: Màn hình 7 đoạn

- Bước 15: Lựa chọn cuối cùng

- Bước 16: Thiết bị bên ngoài: DAC

- Bước 17: Thiết bị bên ngoài: Loa

- Bước 18: Video Demo

- Bước 19: Mã VHDL

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:36.

- Sửa đổi lần cuối 2025-01-23 15:15.

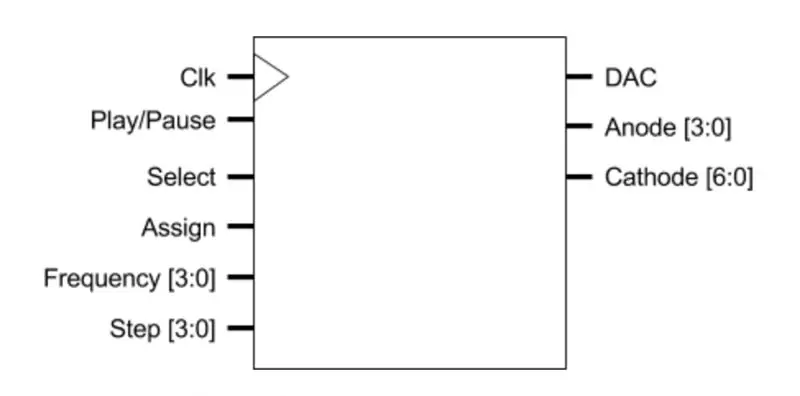

CPE 133, Cal Poly San Luis Obispo

Người tạo dự án: Jayson Johnston và Bjorn Nelson

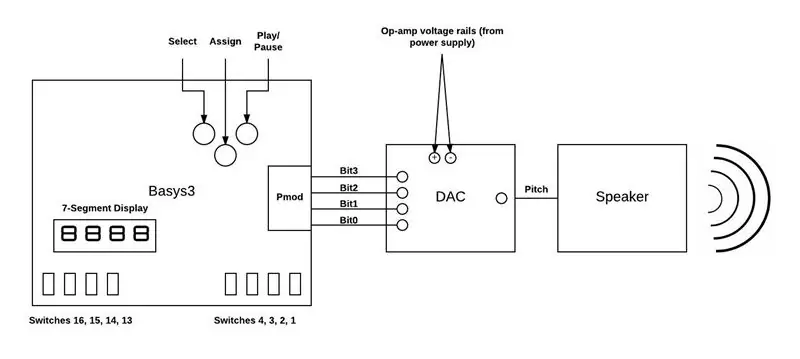

Trong ngành công nghiệp âm nhạc ngày nay, một trong những "nhạc cụ" được sử dụng phổ biến nhất là bộ tổng hợp kỹ thuật số. Mọi thể loại âm nhạc, từ hip-hop đến pop và thậm chí cả nhạc đồng quê, đều sử dụng bộ tổng hợp kỹ thuật số trong phòng thu để tạo ra nhịp điệu và âm thanh mà họ cần để đưa âm nhạc của họ trở nên sống động. Trong hướng dẫn này, chúng tôi sẽ tạo một bộ tổng hợp rất đơn giản với bảng FPGA Basys 3.

Bộ tổng hợp sẽ có thể chơi bốn nốt quý đã chọn với số nhịp không đổi mỗi phút. Người dùng sẽ sử dụng các công tắc để chỉ định mỗi nốt quý cho một cao độ âm nhạc. Đối với dự án này, chúng tôi đang sử dụng bộ chuyển đổi tín hiệu số sang tín hiệu tương tự (DAC) 4 bit để lấy đầu ra từ bo mạch và chuyển nó thành tín hiệu tương tự. Đầu ra từ DAC sau đó sẽ được đưa đến một loa máy tính tiêu chuẩn, tạo ra âm nhạc của chúng ta. Có thể có mười sáu cao độ rời rạc. Chúng tôi sẽ giới hạn bộ tổng hợp của mình ở một quãng tám duy nhất gồm 12 nốt, rơi vào khoảng giữa C (261,6 Hz) và B4 (493,9 Hz). Người dùng cũng sẽ có tùy chọn gán nhiều nốt cùng một lúc, cũng như gán phần còn lại bằng cách nhấn gán trong khi không có nút chuyển cao độ nào được chuyển lên trên. Khi mỗi nốt nhạc được chọn và đang được phát, nốt chữ cái sẽ được hiển thị trên màn hình 7 đoạn. Chúng tôi cũng sẽ sử dụng ba trong số các nút trên bảng, một để phát và tạm dừng nhạc, một để đặt lại bộ tổng hợp và đưa nó vào chế độ “lựa chọn” và nút thứ ba để ấn định cao độ cho mỗi nốt khi ở chế độ chọn.

Khi người dùng hài lòng với lựa chọn ghi chú của họ và sau khi nhấn nút phát, bộ tổng hợp sẽ phát từng nốt liên tiếp cho đến khi người dùng nhấn tạm dừng hoặc chọn.

Dưới đây là danh sách các thiết bị cần thiết:

- Vivado (hoặc bất kỳ không gian làm việc VHDL nào)

- Basys 3 hoặc bảng FPGA tương tự

- Bộ chuyển đổi kỹ thuật số sang tương tự (tối thiểu 4-bit)

- Loa có giắc cắm tai nghe

- Dây dẫn

Bước 1: Thao tác của người dùng với Digital Sequencer

Các bước sau đây là vận hành bộ tuần tự kỹ thuật số. Bộ tuần tự kỹ thuật số hỗ trợ phát lại 12 cao độ riêng biệt (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), trong khoảng từ 261,6 Hz đến 493,9 Hz.

1. Nhấn nút bên trái để đưa bảng vào chế độ lựa chọn. Khi ở chế độ này, 4 công tắc ngoài cùng bên trái (công tắc từ 13 đến 16), mỗi công tắc sẽ được sử dụng để lưu trữ một giá trị cao độ riêng biệt.

2. Để thực hiện lựa chọn, hãy bật một trong các công tắc bên trái, sau đó sử dụng 4 công tắc ngoài cùng bên phải (công tắc từ 1 đến 4) để chọn cao độ mong muốn. Cao độ được kết hợp với một tổ hợp cụ thể của các công tắc phải sẽ được hiển thị trên màn hình bảy phân đoạn và màn hình sẽ cập nhật cao độ liên quan mới bất cứ khi nào các công tắc phải được chuyển sang một tổ hợp mới. Phần còn lại có thể được chỉ định bằng cách không bao giờ chỉ định cao độ cho một trong các công tắc bên trái hoặc bằng cách chỉ định cao độ được hiển thị là 0 trên màn hình cho nốt nhạc. Khi cao độ mong muốn đã được tìm thấy và hiển thị trên màn hình, hãy nhấn nút gán dưới cùng để gán cao độ cụ thể đó cho nốt nhạc.

3. Lặp lại bước 2 cho ba nốt còn lại, bằng cách bật riêng từng công tắc bên trái còn lại, chọn cao độ tương ứng bằng các công tắc bên phải và nhấn nút dưới cùng để gán cao độ cho ghi chú. Nhiều nốt có thể được gán cùng một cao độ bằng cách dịch chuyển nhiều hơn một trong các công tắc trái lên trên cùng một lúc.

4. Bây giờ tất cả các cao độ nốt nhạc đã được ấn định, bộ thu âm kỹ thuật số đã sẵn sàng để chơi. Để phát các nốt trên loa, bạn chỉ cần nhấn nút phát / tạm dừng bên phải để bắt đầu phát nhạc. Thứ tự của trình tự phát lại phản ánh các cao độ được liên kết với các công tắc bên trái, từ trái sang phải. Các nốt sẽ được chơi với một số nhịp nhất định trong một phút, theo thứ tự 1, 2, 3, 4, 1, 2…. Màn hình sẽ hiển thị ghi chú hiện đang phát khi loa phát nhạc. Để tạm dừng phát nhạc, chỉ cần nhấn nút bên phải, sau đó nhạc sẽ ngừng phát và biểu tượng tạm dừng sẽ hiển thị trên màn hình. Nhấn lại nút bên phải sẽ tiếp tục phát lại.

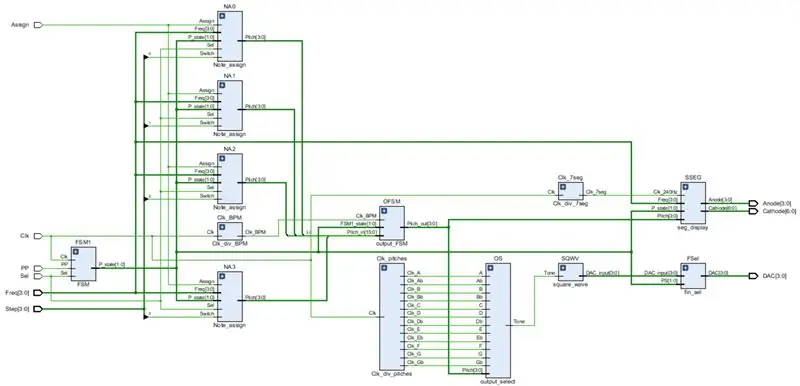

Bước 2: Chi tiết kỹ thuật

Bộ tổng hợp của chúng tôi sử dụng nhiều thành phần kỹ thuật số khác nhau. Bao gồm các máy trạng thái hữu hạn, thanh ghi, bộ ghép kênh, bộ chia đồng hồ và hơn thế nữa. Để xây dựng bộ tổng hợp của mình, chúng tôi đã sử dụng 10 tệp mô-đun duy nhất. Thay vì đặt mỗi mô-đun thành một thành phần, chúng tôi đã chia nhỏ các tệp mô-đun theo chức năng. Do đó, hầu hết các mô-đun đều có nhiều hơn một thành phần. Lưu ý rằng hình ảnh ở trên cho thấy mọi khối được gắn với nhau trong thiết kế hàng đầu của chúng tôi.

Chúng ta sẽ thảo luận về từng mô-đun bằng cách mô tả các đầu vào và đầu ra, chia nhỏ các thành phần của nó và giải thích mục đích của nó trong thiết kế tổng thể. Một tệp ZIP được bao gồm ở cuối tệp hướng dẫn, chứa mọi tệp mã VHDL được sử dụng trong dự án.

Đầu vào

- Clk (tín hiệu đồng hồ gốc)

- PP (phát / tạm dừng)

- Sel (đặt bộ tổng hợp ở chế độ lựa chọn)

- Chỉ định (chỉ định một bước cho một quảng cáo chiêu hàng)

- Bước (ghi chú vị trí)

- Freq (các công tắc tạo cao độ mong muốn)

Kết quả đầu ra

- Cực dương (cực dương 7 đoạn)

- Cathode (catốt 7 đoạn)

- DAC (4-bit điều khiển DAC)

Bước 3: Chi tiết kỹ thuật

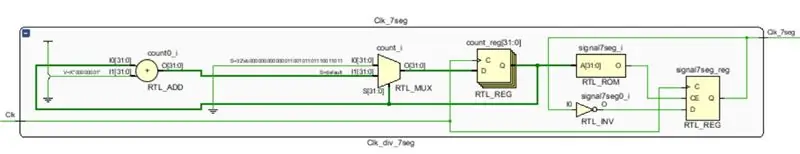

Bước 4: Bộ chia đồng hồ 7 đoạn

Bộ tổng hợp của chúng tôi sử dụng ba bộ chia xung nhịp, tất cả đều tạo ra tín hiệu phục vụ một mục đích khác trong dự án của chúng tôi. Bộ chia đồng hồ lấy tín hiệu đồng hồ gốc và tạo ra tín hiệu đã thay đổi có tần số nhỏ hơn tín hiệu đồng hồ ban đầu. Đồng hồ gốc của Basys 3 là 100 MHz. Đây là tần số mà bộ chia đồng hồ của chúng tôi sử dụng. Nếu bạn đang sử dụng bảng FPGA khác với tần số xung nhịp gốc khác, bạn có thể phải thay đổi mã.

Bộ chia đồng hồ 7 đoạn tạo ra tín hiệu điều khiển tệp seg_display. Chúng tôi sẽ giải thích cách thức hoạt động của tệp này chi tiết hơn khi chúng ta đến phần của nó. Về cơ bản, bộ chia đồng hồ này tạo ra tín hiệu 240 Hz sẽ được sử dụng để chuyển đổi giữa cực dương và cực âm trên màn hình. Tín hiệu là 240 Hz vì tần số mà mắt người không thể nhận biết khi thiếu ánh sáng là 60 Hz. Chúng tôi đang sử dụng hai chữ số, vì vậy bằng cách tăng gấp đôi tần số này, mỗi chữ số sẽ dao động ở tần số 60 Hz. Sau đó, chúng tôi nhân đôi nó để có được 240 Hz vì hệ thống chỉ thay đổi khi tín hiệu đi lên cao, không phải khi tín hiệu xuống thấp.

Để đạt được điều này, bộ chia lấy tín hiệu 100 MHz gốc và đếm lên trên mọi cạnh tăng. Khi bộ đếm đạt đến 416667, đầu ra sẽ đi từ thấp đến cao, hoặc ngược lại.

Đầu vào

Clk (tín hiệu đồng hồ gốc)

Kết quả đầu ra

Clk_7seg (sang seg_display)

Các thành phần

- D đăng ký

- MUX

- Biến tần

- Adder

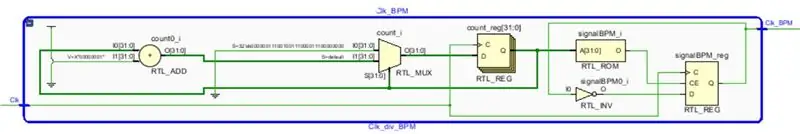

Bước 5: Nhịp đập mỗi phút đồng hồ chia

Bộ chia đồng hồ BPM hoạt động theo cách tương tự. Bộ chia này tạo ra tần số xung nhịp giúp thúc đẩy việc chuyển đổi giữa bốn bước khi xuất âm ở trạng thái phát. Chúng tôi quyết định chuyển đổi giữa các ghi chú ở 100 BPM. Ở 100 BPM, mỗi nốt nhạc sẽ được phát trong 3/5 giây. Tín hiệu thu được sẽ có tần số 1,67 Hz.

Để tạo ra tín hiệu có tần số này, chúng tôi lại sử dụng một hệ thống đếm, nhưng lần này số lượng là 60 triệu. Mỗi khi bộ đếm đạt 60 triệu, tín hiệu đầu ra sẽ chuyển sang mức cao hoặc thấp.

Đầu vào

Clk (tần số đồng hồ gốc)

Kết quả đầu ra

Clk_BPM (đến output_FSM)

Các thành phần

- D đăng ký

- MUX

- Biến tần

- Adder

Bước 6: Pitch dải phân cách đồng hồ

Bộ chia đồng hồ Pitches là bộ chia đồng hồ lớn nhất trong số các bộ chia đồng hồ của chúng tôi. Bộ chia này xuất ra 12 tín hiệu khác nhau tương ứng với 12 nốt nhạc khác nhau mà bộ tổng hợp của chúng tôi có thể phát. Sử dụng kiến thức cơ bản về lý thuyết âm nhạc, chúng tôi suy ra rằng một bit hoặc bus có thể dao động với tốc độ tương ứng với tần số của các nốt nhạc. Để xem các tần số chúng tôi đã sử dụng, hãy xem tại đây. Chúng tôi đã sử dụng quãng tám thứ tư của cao độ.

Hệ thống đếm tương tự được sử dụng ở đây. Để biết các giá trị cụ thể mà chúng tôi đã tính đến, hãy xem tệp có nhãn Clk_div_pitches.

Đầu vào

Clk (tần số đồng hồ gốc)

Kết quả đầu ra

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (đến output_select)

Các thành phần

- D đăng ký

- MUX

- Biến tần

- Adder

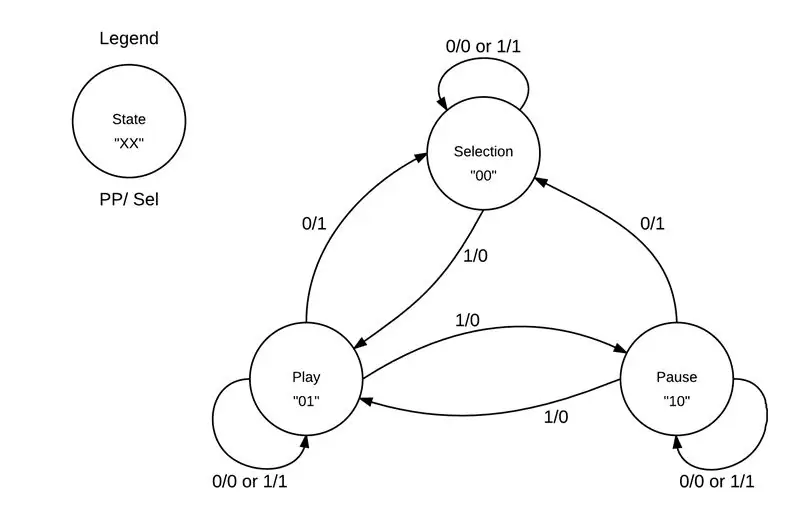

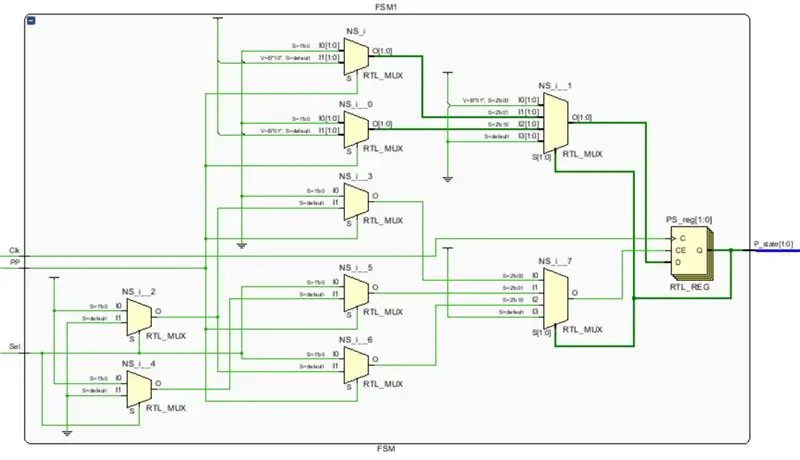

Bước 7: Phát / Tạm dừng / Chọn trạng thái Máy

Trong dự án của chúng tôi có hai máy trạng thái hữu hạn (FSM). FSM là một thiết bị logic chỉ có thể tồn tại ở một trạng thái trong số lượng hữu hạn các trạng thái. Sử dụng FSM, một mạch kỹ thuật số có thể chuyển sang trạng thái mới dựa trên sự kết hợp của các đầu vào. Sử dụng logic đầu vào, trạng thái của FSM sẽ thay đổi khi có một cạnh tăng của đồng hồ. Từ trạng thái và các đầu vào vào mạch, bạn có thể tạo logic đầu ra cung cấp các đầu ra chỉ tồn tại nếu FSM ở một trạng thái nhất định.

Máy trạng thái PPS là FSM đầu tiên trong mạch của chúng tôi. Có ba trạng thái trong FSM này; Chế độ Phát, Tạm dừng và Lựa chọn. Để chuyển qua các trạng thái khác nhau, chúng tôi sử dụng các nút PP và Selection. Xem biểu đồ trạng thái ở trên để biết quá trình chuyển đổi giữa các trạng thái xảy ra như thế nào. Chúng tôi đã thực hiện quá trình chuyển đổi FSM này trên cạnh tăng của xung nhịp 100 MHz gốc, để máy không thể chuyển đổi khi một trong các nút được nhấn, ngay cả trong một khoảng thời gian rất ngắn. Trạng thái hiện tại (P_state) là đầu ra duy nhất từ mô-đun này.

Đầu vào

- Clk (tần số đồng hồ gốc)

- Sel (nút bên trái)

- PP (nút bên phải)

Kết quả đầu ra

P_state (trạng thái hiện tại, thành output_FSM, note_assign, seg_dsiplay, final_select)

Các thành phần

- MUX

- D đăng ký

Bước 8: Phát / Tạm dừng / Chọn trạng thái máy

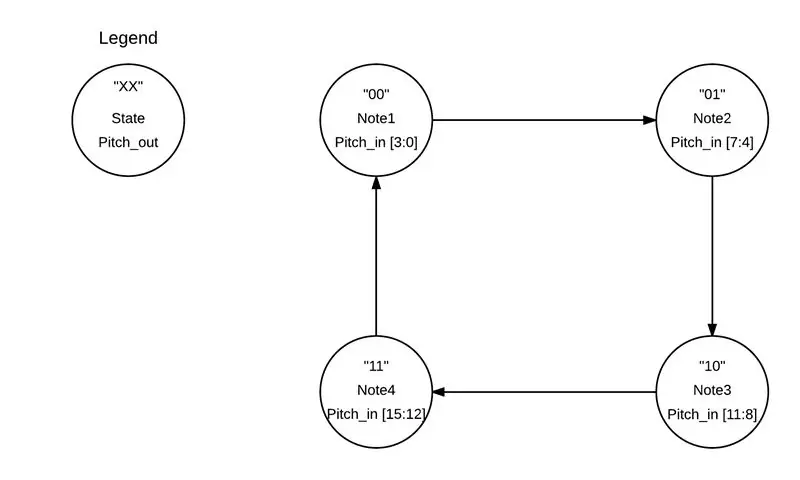

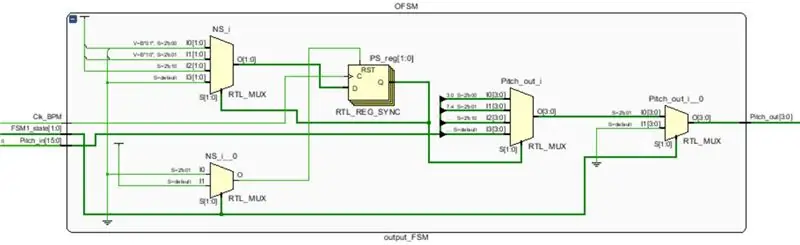

Bước 9: Đầu ra FSM

Đây là FSM thứ hai được tham chiếu trong phần trước. FSM này phục vụ một chức năng khác với chức năng kia, nhưng cơ sở cho chức năng này về cơ bản là giống nhau.

FSM đầu ra chỉ hoạt động nếu trạng thái hiện tại từ FSM đầu tiên là "01" (trạng thái phát). Về cơ bản, đây là kích hoạt cho mô-đun. Nếu trạng thái là "01", thì FSM sẽ chuyển đổi giữa các trạng thái trên cạnh lên của tín hiệu đồng hồ BPM. Chúng tôi làm điều này bởi vì output_FSM đang kiểm soát số nhị phân nào cho cao độ đã chọn sẽ được gửi đến mô-đun output_select và seg_display. FSM có đầu vào 16 bit đến từ mô-đun gán ghi chú, sẽ được đề cập tiếp theo. Ở trạng thái "00" cho output_FSM, mô-đun sẽ xuất "xxxx" cho nốt đầu tiên được gán. Sau đó, trong "01", nó sẽ xuất ra "yyyy" cho nốt thứ hai và cứ tiếp tục như vậy cho mỗi nốt trước khi quay lại nốt đầu tiên. Xem sơ đồ trạng thái ở trên.

FSM này khác với FSM đầu tiên vì không có logic đầu vào để điều khiển chuyển đổi giữa các trạng thái. Thay vào đó, FSM sẽ chỉ hoạt động khi trạng thái từ FSM đầu tiên là "01", và sau đó FSM này sẽ chỉ chuyển đổi giữa các trạng thái trên cạnh lên của tín hiệu đồng hồ. Một sự khác biệt khác là mô-đun này có logic đầu ra, có nghĩa là nó không xuất ra trạng thái hiện tại, nó xuất ra số nhị phân cho cao độ ở trạng thái đó.

Đầu vào

- Clk_BPM (tín hiệu đồng hồ BPM từ bộ chia đồng hồ)

- FSM1_state (PS từ PPS FSM)

- Pitch_in (cao độ từ note_assign)

Kết quả đầu ra

Pitch_out (mỗi lần một cao độ, để output_select và seg_display)

Các thành phần

- MUX

- D đăng ký

Bước 10: Đầu ra FSM

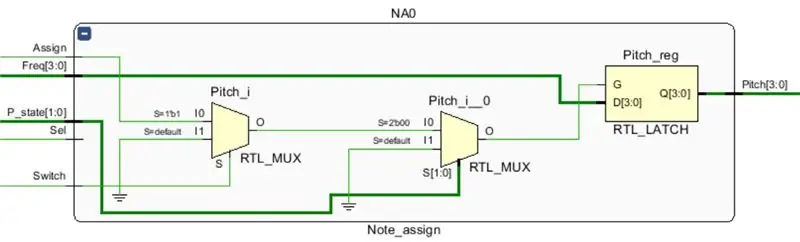

Bước 11: Gán ghi chú

Mô-đun gán nốt có trách nhiệm thực sự gán cao độ cho nốt vị trí hoặc bước. Mô-đun này thực sự khá đơn giản. Đầu tiên, nó kiểm tra xem mạch có ở trạng thái "lựa chọn" hay không và công tắc bước (ngoài cùng bên trái) có cao hay không. Nếu điều này là đúng và nút gán được nhấn, đầu ra của mô-đun sẽ bằng số nhị phân được đại diện bởi các công tắc tần số (ngoài cùng bên phải).

Ban đầu, chúng tôi đã cố gắng tạo ra một mô-đun thực sự lưu một trong các tín hiệu đồng hồ cao độ vào đầu ra, nhưng chúng tôi đã gặp vấn đề với đầu ra thay đổi theo tín hiệu đồng hồ đầu vào. Đây là mô-đun duy nhất được sử dụng nhiều hơn một lần trong thiết kế cuối cùng. Mỗi bước đều có một mô-đun note_assign được liên kết với nó và do đó, mỗi phiên bản của mô-đun nhận được một bit của xe buýt Bước.

Đầu vào

- P_state (trạng thái hiện tại từ PPS FSM)

- Sel (nút bên trái)

- Chuyển đổi (chuyển đổi một bước)

- Freq (công tắc ngoài cùng bên phải cho cao độ)

- Chỉ định (nút dưới cùng, chỉ định một ghi chú)

Kết quả đầu ra

Pitch (số nhị phân, tới output_FSM)

Các thành phần

- MUX

- D đăng ký lại

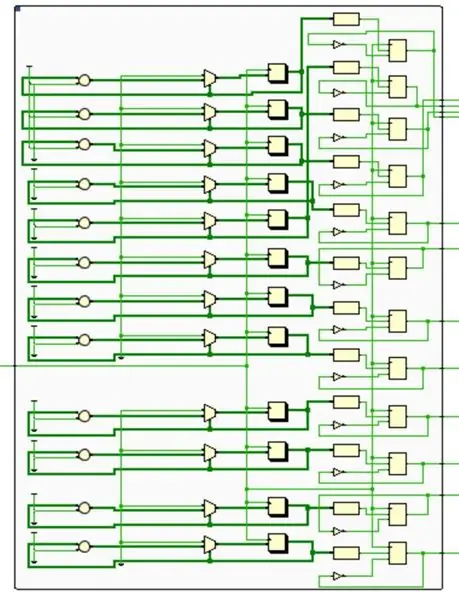

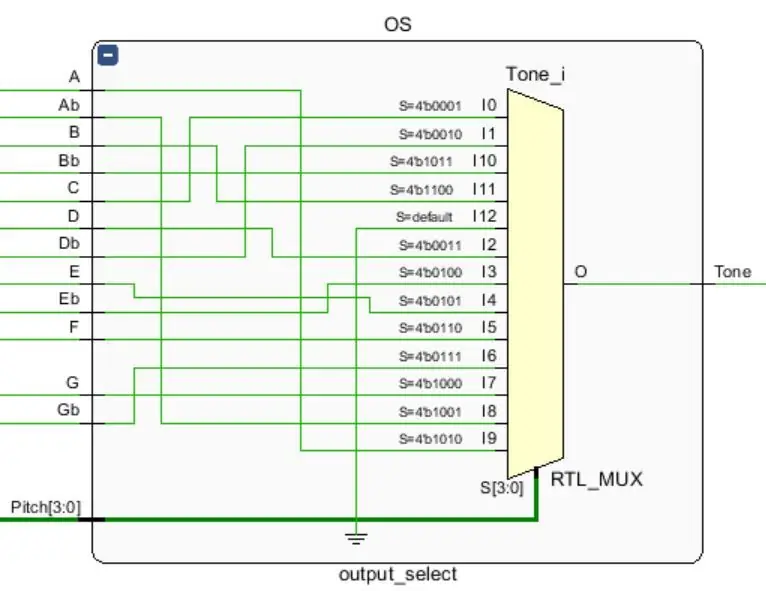

Bước 12: Chọn đầu ra

Lựa chọn đầu ra chịu trách nhiệm lấy số nhị phân cho một cao độ và kết nối số đó với tín hiệu đồng hồ tương ứng của nó. Mặc dù kích thước của nó, đây cũng là một mô-đun tương đối đơn giản. Output_select thực chất là một bộ giải mã nhị phân, giải mã số nhị phân cho một cao độ thành một tín hiệu đồng hồ cụ thể. Trên thực tế, việc gán đầu ra cho tần số đồng hồ hoạt động tốt hơn ở đây so với mô-đun note_assign, bởi vì tất cả những gì mô-đun này phải làm là MUX tín hiệu đồng hồ với số nhị phân đại diện cho đầu vào điều khiển.

Chúng tôi xin lỗi vì việc định tuyến kỳ lạ, Vivado đã sắp xếp các tín hiệu cao độ theo thứ tự bảng chữ cái cho tệp clk_div_pitches, nhưng đối với tệp này, nó đã sắp xếp chúng theo số nhị phân tăng dần, khiến các cao độ theo một thứ tự khác. Cũng lưu ý rằng nếu số nhị phân từ output_FSM là "0000" hoặc bất kỳ thứ gì lớn hơn "1100", thì MUX sẽ gửi qua tín hiệu '0' bằng phẳng.

Đầu vào

- Pitch (từ output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (tín hiệu đồng hồ cao độ)

Đầu ra

Giai điệu (một bit duy nhất khớp với tín hiệu đồng hồ đã chọn, thành square_wave)

Các thành phần

MUX

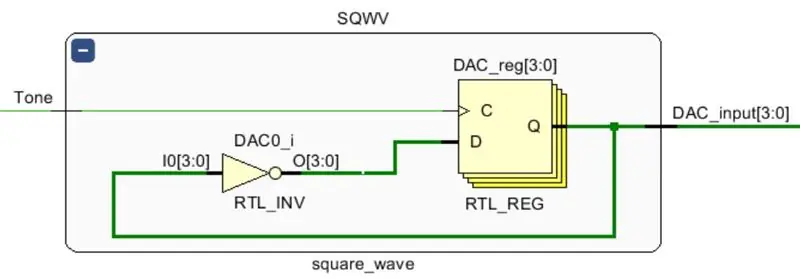

Bước 13: Thế hệ sóng vuông

Mô-đun square_wave là bộ tạo sóng vuông được xuất từ bo mạch đến DAC. Sử dụng tín hiệu âm thanh từ tệp trước đó, square_wave này đảo ngược số 4 bit giữa "0000" và "1111" trên cạnh tăng của Tone. Giai điệu là một tần số cao độ cụ thể, do đó, square_wave tạo ra một sóng có tần số khác khi output_FSM chuyển sang trạng thái khác. Đầu ra 4 bit từ mô-đun này chuyển đến mô-đun fin_sel, nơi logic quyết định liệu bus này có được xuất ra hay không dựa trên trạng thái từ PPS FSM.

Một giải pháp thay thế cho máy phát sóng vuông này là tạo ra sóng hình sin. Mặc dù điều này rất có thể sẽ tạo ra giai điệu cuối cùng tốt hơn, nhưng nó khó thực hiện hơn đáng kể, vì vậy chúng tôi đã chọn chỉ tạo ra một làn sóng vuông.

Đầu vào

Giai điệu (bit dao động từ output_select)

Kết quả đầu ra

DAC_input (bus 4 bit dao động thay đổi ở cùng tần số âm)

Các thành phần

- Biến tần

- D đăng ký

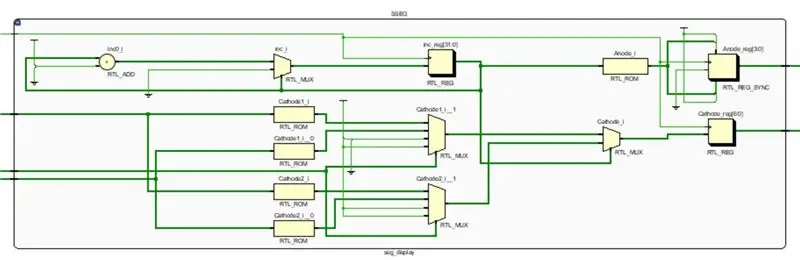

Bước 14: Màn hình 7 đoạn

Mô-đun seg_display điều khiển màn hình 7 đoạn trên bảng nền của chúng tôi. Trong mô-đun, hai quá trình xảy ra. Quá trình đầu tiên giải mã Freq khi ở trạng thái "lựa chọn" hoặc Pitch khi ở chế độ "chơi". Trong chế độ "tạm dừng", mô-đun giải mã để hiển thị biểu tượng tạm dừng. Nhìn vào mã VHDL, bạn có thể thấy rằng bộ giải mã nhị phân thực sự giải mã đầu vào thành hai tín hiệu khác nhau, cathode1 và cathode2. Cathode1 đại diện cho chữ cái tương ứng với cao độ được hiển thị và cathode2 đại diện cho ký hiệu phẳng (b) nếu có. Lý do cho điều này liên quan đến quá trình thứ hai được thực hiện bởi mô-đun seg_display.

Trên bảng basys3, màn hình hiển thị phân đoạn có các cực âm chung. Trong khi cực dương kiểm soát chữ số nào được bật, thì cực âm kiểm soát phân đoạn nào đang bật. Vì màn hình có các cực âm chung, điều đó có nghĩa là bạn chỉ có thể hiển thị một tập hợp các phân đoạn tại một thời điểm. Điều đó đặt ra một vấn đề cho dự án này vì chúng tôi muốn hiển thị một chữ cái ở chữ số đầu tiên và biểu tượng phẳng, nếu cần, cùng một lúc. Bây giờ hãy nhớ tín hiệu đồng hồ 7seg? Để giải quyết vấn đề này, chúng tôi thay đổi các cực dương và cực âm qua lại trên tín hiệu đồng hồ 7seg. Bởi vì tín hiệu đồng hồ là 240 Hz và chúng tôi đang sử dụng hai chữ số, mỗi chữ số sẽ dao động ở 60 Hz. Đối với mắt người, nó sẽ trông giống như các chữ số không hề dao động.

Cũng lưu ý rằng màn hình bảng basys3 sử dụng logic âm. Điều này có nghĩa là nếu một cực dương hoặc cực âm được đặt thành '0', chữ số hoặc đoạn đó sẽ được bật và ngược lại.

Đầu vào

- Pitch (số nhị phân cho một nốt nhạc, được sử dụng ở trạng thái phát)

- Freq (công tắc tần số, được sử dụng khi ở trạng thái lựa chọn)

- P_state (trạng thái hiện tại từ PPS FSM)

- Clk_240Hz (tín hiệu xung nhịp từ Clk_div_7seg, gấp đôi 120 vì chúng tôi chỉ sử dụng cạnh tăng)

Kết quả đầu ra

- Cathode (bus điều khiển các phân đoạn trên màn hình, đầu ra cuối cùng)

- Anode (bus điều khiển các chữ số trên màn hình, đầu ra cuối cùng)

Các thành phần

- Chốt cửa

- MUX

- D đăng ký

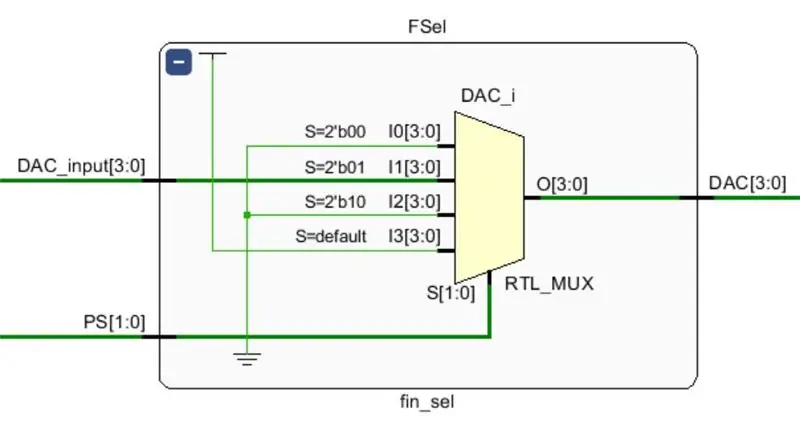

Bước 15: Lựa chọn cuối cùng

Lựa chọn cuối cùng là mô-đun cuối cùng được sử dụng trong dự án này. Một mô-đun đơn giản khác, mô-đun này điều khiển đầu ra cuối cùng sẽ đến DAC. Khi ở trạng thái "lựa chọn" hoặc "tạm dừng", mô-đun sẽ xuất ra "0000" tĩnh để không có nhạc nào được phát từ loa. Ở trạng thái "phát", mô-đun sẽ xuất ra 4 bit dao động như được xác định bởi square_wave.

Đầu vào

- P_state (trạng thái hiện tại từ PPS FSM)

- DAC_input (4-bit dao động từ square_wave)

Kết quả đầu ra

DAC (bằng DAC_input ở trạng thái phát, đầu ra cuối cùng)

Các thành phần

MUX

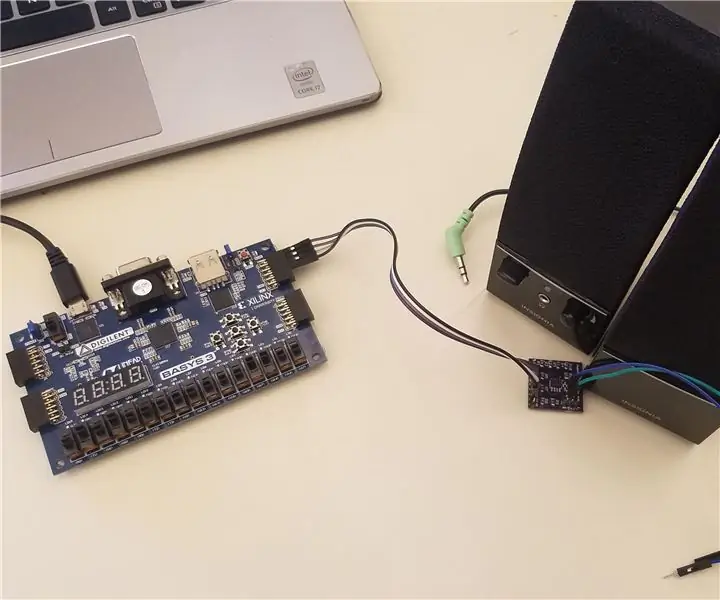

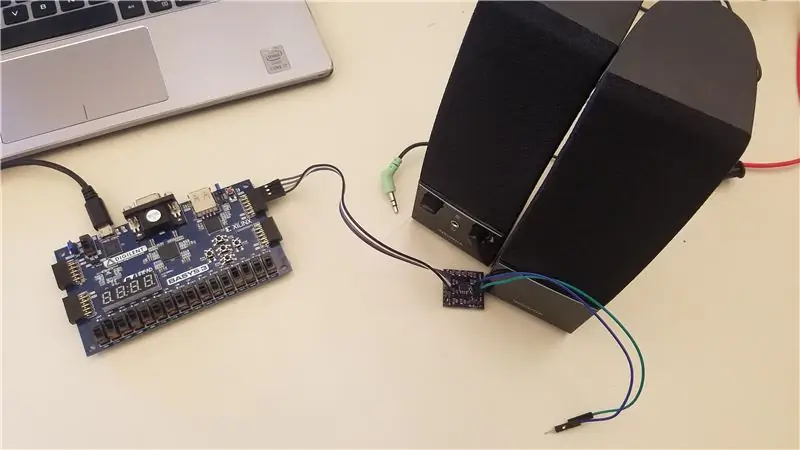

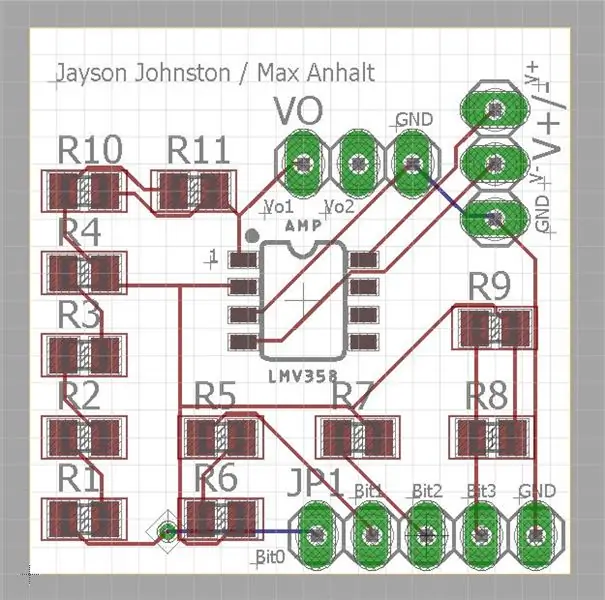

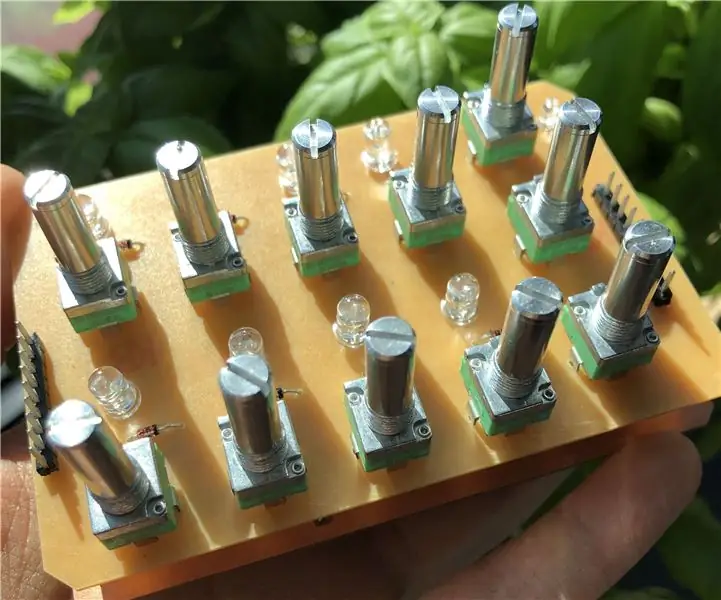

Bước 16: Thiết bị bên ngoài: DAC

Bộ chuyển đổi tín hiệu số sang tín hiệu tương tự (DAC) lấy tín hiệu rời rạc và chuyển thành tín hiệu liên tục. DAC của chúng tôi có bốn bit và được làm từ một bộ khuếch đại tổng hợp. Bằng cách sử dụng một tỷ lệ điện trở trong vòng cung cấp và phản hồi, chúng tôi có thể tạo ra một hệ thống đầu ra ở 16 mức khác nhau được tạo ra bằng cách "tính tổng" của mỗi nhánh. Bit0, nhánh trên cùng, mang trọng lượng nhỏ nhất và đóng góp thế năng nhỏ nhất khi cao vì nhánh đó có sức đề kháng cao hơn. Trọng lượng tăng lên khi bạn đi xuống các cành cây. Nếu bạn đếm trong hệ nhị phân lên và sau đó giảm xuống bằng cách sử dụng các đầu vào bit, thì điện áp đầu ra sẽ giống như một bước sóng sin khôn ngoan. Đầu vào của DAC được kết nối với một trong các PMOD trên bo mạch để truyền tín hiệu 4 bit.

DAC ban đầu được lắp ráp cho một lớp Kỹ sư Điện và được thiết kế và hàn bởi chúng tôi, không phải mua từ cửa hàng. Trên đây là hình ảnh của file thiết kế tạo mạch in.

Bước 17: Thiết bị bên ngoài: Loa

Đối với dự án này, bạn sẽ không muốn mua một cặp loa siêu đẹp. Như bạn có thể nói, âm thanh là khá cơ bản. Chúng tôi đã đến và mua một bộ loa máy tính trị giá 8 đô la từ Best Buy. Bất cứ thứ gì có giắc cắm tai nghe đều hoạt động tốt. Monotone cũng hoạt động tốt. Bạn thậm chí có thể sử dụng tai nghe, nhưng bạn có thể làm hỏng chúng!

Để kết nối đầu ra của DAC với loa, chúng tôi sử dụng cáp jumper và sau đó giữ cáp đầu ra vào đầu giắc cắm tai nghe và cáp nối đất với đế. Chúng tôi đã thử sử dụng băng dính điện để giữ các dây cáp tại chỗ, nhưng nó gây ra rất nhiều nhiễu. Thử một kiểu băng khác có thể giải quyết được vấn đề này.

Đối với loa của chúng tôi, chúng tôi đã chuyển chúng sang cài đặt cao nhất và có tiếng ồn lớn.

Và đó là bước cuối cùng để tạo bộ tuần tự kỹ thuật số từ bảng FPGA! Chuyển đến hai phần tiếp theo để tải xuống tất cả mã VHDL của chúng tôi và xem trình tự sắp xếp hoạt động.

Bước 18: Video Demo

Video này cho thấy phiên bản cuối cùng của dự án làm việc, bao gồm quá trình chỉ định các nút chuyển cho 4 cao độ riêng biệt và các diễn giả phát các nốt tương ứng.

Bước 19: Mã VHDL

Đây là mã cho toàn bộ dự án, bao gồm tệp ràng buộc và tệp sim được sử dụng trong khi xây dựng trình tự sắp xếp. Lưu ý rằng các tệp thiết kế không sử dụng nói như vậy trong kiến trúc.

Đề xuất:

Arduino MIDI Rhythm Section Sequencer: 8 Step (with Hình ảnh)

Arduino MIDI Rhythm Section Sequencer: Ngày nay có một máy đánh trống phần mềm tốt rất dễ và rẻ nhưng sử dụng chuột giết chết niềm vui đối với tôi. Đây là lý do tại sao tôi nhận ra những gì ban đầu được dự định là một bộ xử lý trống MIDI phần cứng 64 bước thuần túy có khả năng kích hoạt tới 12 độ cao trống khác nhau

Parallel Sequencer Synth: 17 bước (có hình ảnh)

Parallel Sequencer Synth: Đây là hướng dẫn tạo một trình tự đơn giản. Bộ tuần tự là một thiết bị tạo ra một loạt các bước theo chu kỳ, sau đó điều khiển một bộ dao động. Mỗi bước có thể được gán cho một giai điệu khác nhau và do đó tạo ra các chuỗi hoặc hiệu ứng âm thanh thú vị.

Atari Punk Console With a Baby 8 Step Sequencer: 7 Step (with Pictures)

Atari Punk Console Với Baby 8 Step Sequencer: Phiên bản trung gian này là Atari Punk Console tất cả trong một và Baby 8 Step Sequencer mà bạn có thể sử dụng trên Máy phay PCB trên Bantam Tools Desktop. Nó được tạo thành từ hai bảng mạch: một bảng là bảng giao diện người dùng (UI) và bảng còn lại là bo mạch tiện ích

Máy ảnh hồng ngoại hình ảnh nhiệt tự làm: 3 bước (có hình ảnh)

Máy ảnh hồng ngoại hình ảnh nhiệt tự làm: Xin chào! Tôi luôn tìm kiếm các Dự án mới cho các bài học vật lý của mình. Hai năm trước, tôi đã xem một báo cáo về cảm biến nhiệt MLX90614 từ Melexis. Loại tốt nhất chỉ với 5 ° FOV (trường nhìn) sẽ phù hợp với máy ảnh nhiệt tự chế

Ánh sáng video thân mật / Ánh sáng chụp ảnh cầm tay: 7 bước (với hình ảnh)

Ánh sáng video thân mật / Ánh sáng chụp ảnh cầm tay: Tôi biết bạn đang nghĩ gì. Bằng cách " thân mật, " Ý tôi là chiếu sáng cận cảnh trong các tình huống ánh sáng khó - không nhất thiết dành cho " các tình huống thân mật. &Quot; (Tuy nhiên, nó cũng có thể được sử dụng cho việc đó …) Là một nhà quay phim thành phố New York - hoặc