Mục lục:

- Bước 1: Sơ đồ khối

- Bước 2: Nguyên lý hoạt động

- Bước 3: Triển khai logic

- Bước 4: Giải quyết bế tắc

- Bước 5: Cấu hình thiết bị - Mạch Matrix0

- Bước 6: Cấu hình thiết bị - Logic đóng gói SPI

- Bước 7: Cấu hình thiết bị - Thuộc tính thành phần Matrix0

- Bước 8: Cấu hình thiết bị - Mạch Matrix1

- Bước 9: Cấu hình thiết bị - Bộ đếm nhị phân 3 bit

- Bước 10: Cấu hình thiết bị - Logic so sánh 3-bit

- Bước 11: Cấu hình thiết bị - Logic so sánh kỹ thuật số và Đăng ký tạm thời

- Bước 12: Cấu hình thiết bị - Thuộc tính thành phần Matrix1

- Bước 13: Kết quả

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:31.

- Sửa đổi lần cuối 2025-01-23 15:15.

Hệ thống điều khiển và các thiết bị liên quan xử lý nhiều nguồn điện, chẳng hạn như đường phân cực hoặc pin, và phải theo dõi đường cao nhất (hoặc thấp nhất) trong một bộ nhất định.

Ví dụ: chuyển đổi tải trong hệ thống cấp nguồn “nhiều pin” yêu cầu hệ thống giám sát điện áp tối thiểu hoặc tối đa giữa dãy pin (tối đa hoặc tối thiểu là một chức năng của thuật toán chuyển đổi cụ thể) và tự động định tuyến tải đến nguồn thích hợp nhất trong thời gian thực. Ngoài ra, hệ thống có thể cần tạm thời ngắt kết nối pin có điện áp thấp nhất để sạc thích hợp.

Một ví dụ khác là hệ thống năng lượng mặt trời hiện đại, trong đó mỗi tấm pin mặt trời được trang bị cơ chế chuyển động nghiêng và với một mạch theo dõi năng lượng mặt trời (cái sau cung cấp thông tin vị trí Mặt trời để định hướng tấm pin). Với thông tin về điện áp tối đa, mỗi vị trí bảng điều khiển năng lượng mặt trời có thể được tinh chỉnh trên cơ sở bảng điều khiển của chuỗi thực sự mang lại điện áp đầu ra cao nhất, do đó đạt được mức tối ưu hóa điện năng vượt trội.

Có một số nhãn hiệu khác nhau của IC thương mại (chủ yếu là vi điều khiển) về nguyên tắc có thể triển khai bộ theo điện áp tối đa. Tuy nhiên, chúng yêu cầu lập trình và ít hiệu quả về chi phí hơn so với giải pháp tín hiệu hỗn hợp. Việc bổ sung một thiết kế Dialog GreenPAKTM có thể ảnh hưởng tích cực đến khả năng chi trả, kích thước và tính mô đun của thiết kế. Thiết kế này khai thác lợi ích của việc tích hợp cả mạch tương tự và kỹ thuật số vào một chip duy nhất.

Trong Có thể hướng dẫn này, giao diện người dùng tương tự và logic kỹ thuật số cần thiết để triển khai công cụ tìm điện áp tối đa (hoặc cuối cùng là tối thiểu) trong số tám nguồn riêng biệt được triển khai.

Để triển khai màn hình điện áp tối đa / phút tương tự 8 kênh, sử dụng SLG46620G.

Dưới đây, chúng tôi mô tả các bước cần thiết để hiểu cách giải pháp đã được lập trình để tạo ra màn hình điện áp tối đa / phút tương tự 8 kênh. Tuy nhiên, nếu bạn chỉ muốn lấy kết quả của việc lập trình, hãy tải phần mềm GreenPAK để xem File thiết kế GreenPAK đã hoàn thành. Cắm Bộ phát triển GreenPAK vào máy tính của bạn và nhấn chương trình để tạo màn hình điện áp tối đa / phút tương tự 8 kênh.

Bước 1: Sơ đồ khối

Hình 1 cho thấy sơ đồ toàn cục của hệ thống được triển khai.

Một chuỗi gồm tối đa 8 nguồn điện áp thay đổi được ghép kênh và giao tiếp với mô-đun GreenPAK’s ADC được kết nối với thiết kế bên trong tùy chỉnh có khả năng chọn nguồn có điện áp cao nhất so với các nguồn khác. Logic bên trong xuất ra thông tin này để hiển thị hoặc xử lý thêm.

Thiết kế dựa trên sản phẩm GreenPAK SLG46620G, vì nó nhúng tất cả các khối xây dựng tương tự và kỹ thuật số cần thiết cho ứng dụng. Trong quá trình triển khai này, mảng được quét bằng bộ ghép kênh tương tự ADG508 do IC GreenPAK điều khiển trực tiếp.

Thông tin đầu ra là số kỹ thuật số 3 bit tương ứng với số nguồn điện áp ở điện áp tối đa. Một cách trực tiếp để lấy thông tin này là hiển thị số bằng màn hình 7 đoạn. Có thể dễ dàng thực hiện điều này bằng cách giao tiếp đầu ra kỹ thuật số của SLG46620G với trình điều khiển màn hình 7 đoạn, chẳng hạn như giải pháp GreenPAK được mô tả trong Tài liệu tham khảo hoặc với IC 74LS47 thông thường.

Mạch được trình bày tìm điện áp cực đại. Để chuyển đổi thiết kế thành một công cụ tìm điện áp tối thiểu, phải thêm một mạch điều hòa sơ bộ đơn giản giữa bộ ghép kênh tương tự và đầu vào tương tự GreenPAK, trừ đầu ra của bộ ghép kênh khỏi điện áp tham chiếu 1 V.

Bước 2: Nguyên lý hoạt động

Thiết kế nhằm mục đích chọn nguồn có điện áp tối đa, do đó quá trình quét được thực hiện trên toàn bộ mảng trong khi lưu trữ giá trị tối đa cuối cùng và so sánh nó với giá trị tiếp theo trong đầu vào (thuộc về nguồn điện áp tiếp theo trong quá trình quét).

Trong phần sau, chúng tôi sẽ đề cập đến một chuỗi ghép kênh hoàn chỉnh cùng với tất cả các đầu vào dưới dạng “quét” hoặc “vòng lặp”.

So sánh giữa hai giá trị không được thực hiện bằng các thành phần ACMP (tuy nhiên, có sẵn trong SLG46620G), mà là bằng mô-đun DCMP, sau khi các giá trị tương ứng được số hóa. Đây là một kỹ thuật tiên tiến và tinh tế được đề cập đầu tiên trong Tài liệu tham khảo.

Hình 2 cho thấy SLG46620G được cấu trúc như thế nào cho thiết kế này.

Tín hiệu đầu vào tương tự đi tới đầu vào ADC thông qua thành phần PGA với mức Tăng 1. Nhiều cài đặt Mức tăng khác nhau cũng có thể tìm thấy sự phù hợp nhất với thiết bị điện tử điều hòa phía trước dành để ánh xạ điện áp đầu vào thành 0-1 V phạm vi của mô-đun GreenPAK ADC.

ADC hoạt động ở chế độ một đầu và chuyển đổi tín hiệu tương tự thành mã kỹ thuật số 8-bit, sau đó được chuyển đến mô-đun DCMP. Mã kỹ thuật số cũng được đưa vào khối SPI, được định cấu hình như Bộ đệm ADC / FSM, nơi mã kỹ thuật số có thể được lưu trữ và sẽ không thay đổi cho đến khi xung tiếp theo đến với đầu vào SPI CLK. Lưu ý rằng một khối logic chuyên dụng điều khiển đầu vào SPI CLK. Chúng tôi sẽ điều tra phần này sau, vì đây là logic "cốt lõi" chịu trách nhiệm cho hoạt động thích hợp. Mã kỹ thuật số mới chỉ được lưu trữ vào mô-đun SPI nếu nó thuộc về điện áp đầu vào tối đa thực tế.

Thành phần DCMP được sử dụng để so sánh dữ liệu ADC hiện tại với dữ liệu chiến thắng cuối cùng (đó là giá trị tối đa được tìm thấy cuối cùng) được lưu trữ trong khối SPI. Nó sẽ tạo ra một xung ở đầu ra OUT + khi dữ liệu ADC mới lớn hơn dữ liệu trước đó. Chúng tôi sử dụng tín hiệu OUT + để cập nhật khối SPI với người chiến thắng mới.

Tín hiệu đồng hồ toàn cầu thúc đẩy chuyển đổi ADC và thời gian chung. Sau khi thực hiện chuyển đổi, tín hiệu đầu ra INT của ADC sẽ phát xung, phối hợp kịp thời với đầu ra dữ liệu song song ADC. Chúng tôi cũng sử dụng đầu ra INT để tăng bộ đếm nhị phân 3 bit, được thực hiện bởi các DFF trong Matrix1, hữu ích vì ba lý do:

1. Các đường đầu ra của bộ đếm địa chỉ bộ ghép kênh tương tự bên ngoài, do đó phục vụ điện áp đầu vào tiếp theo cho ADC;

2. Số đếm được cố định vào một thanh ghi 3 bit (được thực hiện trong Matrix1) để lưu trữ người chiến thắng tạm thời trong quá trình quét;

3. Số đếm được giải mã để cập nhật thanh ghi 3 bit thứ hai (được triển khai trong Matrix0) sau khi quá trình quét hoàn tất.

Bước 3: Triển khai logic

Mô-đun ADC tuần tự cung cấp dữ liệu được chuyển đổi của tất cả các điện áp đầu vào, lần lượt, vô thời hạn. Khi Bộ ghép kênh được định địa chỉ 0b111 (số thập phân 7), bộ đếm sẽ chuyển sang 0b000 (số thập phân 0), do đó bắt đầu quét mới các điện áp đầu vào.

Trong quá trình quét, tín hiệu đầu ra ADC INT được tạo ra khi đầu ra dữ liệu song song hợp lệ. Khi tín hiệu này xung, bộ ghép kênh tương tự phải chuyển sang đầu vào tiếp theo, cung cấp cho PGA điện áp tương ứng. Do đó, đầu ra ADC INT là tín hiệu xung nhịp trực tiếp của Bộ đếm nhị phân 3 bit trong Hình 2, mà từ đầu ra song song 3 bit của nó trực tiếp địa chỉ bộ ghép kênh tương tự bên ngoài (“V select” trong Hình 1).

Bây giờ chúng ta hãy tham khảo một ví dụ trong đó điện áp đầu vào được cho là có các mối quan hệ sau:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Hình 3 đại diện cho các tín hiệu chính liên quan đến cơ chế quyết định tối đa.

Vì dữ liệu cuối cùng được đưa vào thanh ghi bộ đệm SPI đồng bộ với các xung INT, một cửa sổ so sánh tồn tại nơi nội dung bộ đệm SPI được so sánh với kết quả chuyển đổi ADC tiếp theo. Thời gian cụ thể này dẫn đến việc tạo ra các xung OUT + ở đầu ra DCMP. Chúng ta có thể tận dụng các xung này để nạp các giá trị mới vào thanh ghi đệm SPI.

Như rõ ràng từ dòng dữ liệu đệm SPI của Hình trước, thanh ghi SPI luôn chứa giá trị lớn nhất theo thời gian, giá trị lớn nhất trong số 8 đầu vào và nó chỉ được cập nhật khi một giá trị lớn hơn được phát hiện bởi mô-đun DCMP (đề cập đến DCMP OUT + dòng đầu ra của âm mưu, các xung bị thiếu làm cho V2 vẫn được chốt trong thanh ghi cho đến khi so sánh với V5).

Bước 4: Giải quyết bế tắc

Nếu logic được triển khai sẽ giống như mô tả ở trên, rõ ràng là chúng ta sẽ gặp phải tình huống bế tắc: hệ thống chỉ có khả năng phát hiện điện áp cao hơn điện áp tương ứng với những gì được lưu trữ trong thanh ghi bộ đệm SPI.

Điều này cũng hợp lệ trong trường hợp điện áp này giảm và sau đó một đầu vào khác, cho đến bây giờ thấp hơn mức đó, trở thành cao nhất: nó sẽ không bao giờ được phát hiện. trong trẻo.

Tại thời điểm lặp 2, V3 giảm xuống và V1 là điện áp tối đa thực tế. Nhưng mô-đun DCMP không cung cấp xung vì dữ liệu được lưu trữ trong thanh ghi bộ đệm SPI (tương ứng với 0,6 V) lớn hơn dữ liệu tương ứng với V1 (0,4 V).

Sau đó, hệ thống hoạt động như một công cụ tìm tối đa "tuyệt đối" và không cập nhật đầu ra một cách chính xác.

Một cách hay để khắc phục vấn đề này là buộc tải lại dữ liệu vào SPI Buffer Register khi hệ thống hoàn thành một chu kỳ thăm dò đầy đủ của tất cả các kênh.

Trên thực tế, nếu điện áp tại đầu vào đó vẫn là cao nhất, không có gì thay đổi và việc điều khiển tiếp tục diễn ra một cách an toàn (xem Hình 4 ở trên, đây là trường hợp của Lặp đi lặp lại 0 và 1). Mặt khác, nếu điện áp tại đầu vào đó tình cờ giảm xuống một giá trị nhỏ hơn một đầu vào khác, thì việc tải lại giá trị sẽ mang lại khả năng cho mô-đun DCMP tạo ra xung OUT + khi so sánh nó với giá trị tối đa mới (đây là trường hợp Lặp lại vòng lặp 2 và 3).

Một đoạn mạch logic là cần thiết để khắc phục sự cố. Nó phải tạo ra một tín hiệu đồng hồ cho thành phần SPI khi vòng lặp đạt đến đầu vào tối đa thực tế, do đó buộc phải tải lại từ dữ liệu cập nhật của nó vào Thanh ghi đệm SPI. Điều này sẽ được thảo luận trong Phần 7.2 và 7.6 dưới đây.

Bước 5: Cấu hình thiết bị - Mạch Matrix0

SLG46620G có hai khối Ma trận, như được mô tả trong Hình 2. Các Hình sau đây cho thấy các cấu hình thiết bị tương ứng.

Phần trên của mạch là “Thanh ghi vòng lặp” được thực hiện với 3 DFF (DFF0, DFF1 và DFF2). Nó được làm mới sau mỗi vòng lặp của bộ ghép kênh đầu vào để gửi đến trình điều khiển hiển thị 7 đoạn số nhị phân của "người chiến thắng", đó là đầu vào có điện áp cao nhất trong lần quét cuối cùng. Cả xung nhịp đến DFF và dữ liệu đều đến từ logic được triển khai trong Matrix1 lần lượt thông qua cổng P12, P13, P14 và P15.

Phần dưới là mặt trước tương tự với đầu vào tại Chân 8 và PGA với độ lợi x1. Đầu ra ADC INT đi tới cả logic xung nhịp của SPI và tới Matrix1 thông qua cổng P0, nơi nó sẽ đóng vai trò là tín hiệu đồng hồ cho bộ đếm được triển khai.

Đầu ra dữ liệu song song ADC và SPI tương ứng có nhãn NET11 và NET15 để được kết nối với thành phần DCMP trong Matrix1.

Bước 6: Cấu hình thiết bị - Logic đóng gói SPI

Như đã chỉ ra trước đây trong phần “Thực thi logic”, Thanh ghi đệm SPI được cập nhật mỗi khi so sánh giữa giá trị được lưu trữ thực tế và dữ liệu chuyển đổi ADC mới tạo ra một xung ở đầu ra DCMP OUT +.

Tính toàn vẹn của tín hiệu được đảm bảo nếu tín hiệu này là AND-ed với đầu ra ADC INT. Điều này tránh bất kỳ sự tăng đột biến và kích hoạt sai.

Chúng tôi cũng nhấn mạnh rằng để bỏ qua các tình huống bế tắc, Bộ đệm SPI phải được cập nhật khi vòng lặp đạt đến dữ liệu người chiến thắng thực tế.

Sau đó, ba tín hiệu trong trò chơi để điều chỉnh tốc độ SPI thích hợp:

1. Đầu ra ADC INT (LUT0-IN1)

2. DCMP OUT + đầu ra (LUT0-IN0 qua cổng P10)

3. Đếm bằng tín hiệu chốt (LUT0-IN2 qua cổng P11)

Hai phần đầu là AND-ed và cả OR-ed với phần sau trong LUT0, có cấu hình triển khai như trong Hình 6.

Bước 7: Cấu hình thiết bị - Thuộc tính thành phần Matrix0

Hình 7-10 cho thấy các cửa sổ thuộc tính các thành phần còn lại thuộc Matrix0.

Bước 8: Cấu hình thiết bị - Mạch Matrix1

Bước 9: Cấu hình thiết bị - Bộ đếm nhị phân 3 bit

Phần trên của mạch chứa các phần tử logic, chủ yếu là bộ đếm nhị phân 3 bit được tạo xung nhịp bởi đầu ra ADC INT, như đã được thảo luận. Bộ đếm này được thực hiện với một sơ đồ khá “chuẩn” được thể hiện trong Hình 12.

Bộ đếm này được hiện thực hóa trong thiết kế của chúng tôi bằng Flip-Flops DFF9, DFF10, DFF11 và INV1, LUT4, LUT8. Đầu ra DFF9 là LSB trong khi DFF11 là MSB như trong Hình 13.

LUT4 được cấu hình như một XOR trong khi LUT8 thực hiện logic AND-XOR của Hình 12.

Đầu ra của bộ đếm đi đến ba chân đầu ra kỹ thuật số để định địa chỉ cho Bộ ghép kênh tương tự bên ngoài.

LUT10 giải mã mã của bộ đếm khi quá trình quét hoàn tất và cấp một xung cho Matrix0 qua DLY8 và cổng P12. Điều này đơn giản được thực hiện bằng cách AND nhập các đầu ra của bộ đếm, do đó giải mã số 7 dec (0b111 nhị phân, kết thúc vòng lặp).

Bước 10: Cấu hình thiết bị - Logic so sánh 3-bit

Hình 15 cho thấy mạch được sử dụng để phát hiện khi nào vòng lặp đang lặp lại ở địa chỉ “thắng cuộc” hiện tại. Trong trường hợp này, như đã thảo luận, một xung kỹ thuật số sẽ buộc tải lại kết quả ADC hiện tại để giải quyết tình huống bế tắc có thể xảy ra.

Địa chỉ “người chiến thắng” được lưu trữ trong thanh ghi tạm thời của Matrix1 (xem bên dưới), trong khi địa chỉ hiện tại được xuất ra bởi bộ đếm nhị phân.

Cổng XNOR cung cấp đầu ra đúng (logic 1 hoặc 'cao') khi cả hai đầu vào bằng nhau. AND-ing tín hiệu này cho tất cả các bit (LUT9) cung cấp cho chúng ta một xung khi cả hai mã nhị phân đều giống nhau. Thông tin chi tiết về cổng XOR như một bộ kiểm tra chẵn lẻ có thể được tìm thấy trong Tài liệu tham khảo.

Tín hiệu ‘Counter-equals-Latch’ được chuyển tới Matrix0 qua cổng P11.

Bước 11: Cấu hình thiết bị - Logic so sánh kỹ thuật số và Đăng ký tạm thời

Phần dưới của Hình 11 (được tô sáng trong Hình 16) cho thấy khối DCMP, phần ra quyết định của thiết kế này.

DFF6, 7 và 8 tạo thành một thanh ghi 3 bit để lưu trữ số đầu vào tạm thời “người chiến thắng” trong khi vòng lặp đang chạy. Đầu vào cho Flip-Flops là các đầu ra bộ đếm nhị phân 3 bit, như có thể nhìn thấy trong mạch Matrix1 toàn cục của Hình 11, ở đây được bỏ qua để rõ ràng hơn.

Đầu ra của thanh ghi này không thể điều khiển trực tiếp màn hình 7 đoạn vì giá trị được lưu trữ ở đây thay đổi trong quá trình quét và chỉ nên được coi là 'hợp lệ' khi kết thúc quá trình quét.

Vì lý do này, các đầu ra thanh ghi tạm thời kết nối với Thanh ghi vòng lặp của Matrix0 thông qua các cổng liên ma trận P13, P14 và P15.

Điều quan trọng là quan sát trong Hình 16 rằng thanh ghi tạm thời được xung nhịp bởi đầu ra DCMP OUT + khi kết quả so sánh các thanh ghi ADC-SPI trong một giá trị tối đa mới được tìm thấy.

Tín hiệu OUT + tương tự được chuyển tới Matrix0, SPI CLK Logic, qua cổng P10.

Bước 12: Cấu hình thiết bị - Thuộc tính thành phần Matrix1

Hình 17-19 cho thấy các cửa sổ thuộc tính thành phần thuộc Matrix1.

Bước 13: Kết quả

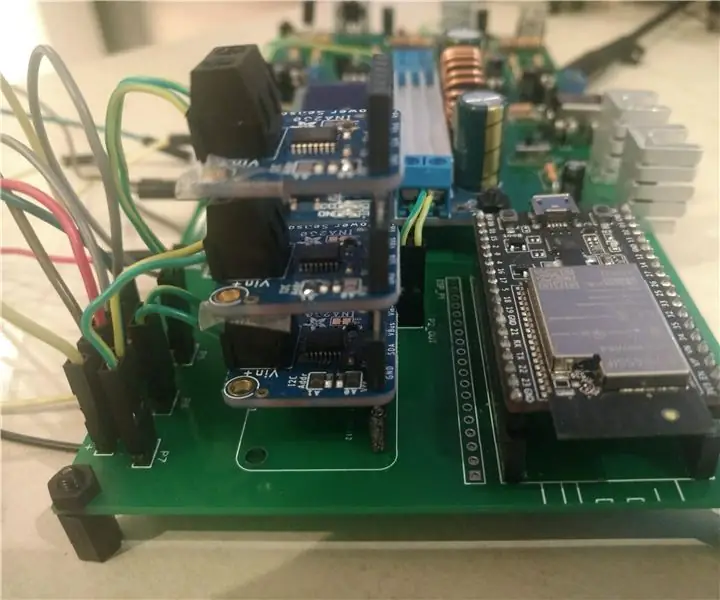

Để kiểm tra việc thực hiện, một nguyên mẫu bảng đánh giá đã được xây dựng, trong đó 8 điện áp đầu vào tương tự thu được bằng một loạt các bộ chia điện trở với TrimPots (như trong Hình 20).

Bộ ghép kênh được sử dụng là ADG508, một bộ phận có thể hoạt động với nguồn cung cấp duy nhất (12 V).

Trình điều khiển màn hình 7 đoạn là 74LS47. Nó giải mã một từ đầu vào song song và trực tiếp điều khiển màn hình 7 đoạn cực dương chung.

Bảng đánh giá có đầu nối góc vuông 2x10 để cắm trực tiếp vào Nền tảng phát triển nâng cao GreenPAK tại đầu nối mở rộng của nó như thể hiện trong Hình 21.

Việc kết hợp với Nền tảng phát triển nâng cao GreenPAK giúp việc đo lường các tín hiệu để kiểm tra nhanh rất đơn giản. Ví dụ: Hình 22 cho thấy một tập hợp các tín hiệu (tương ứng là đầu ra CLOCK, ADC INT và đầu ra DCMP OUT +) được thu bởi Máy phân tích logic HP 54620A. Dạng sóng được kích hoạt bởi một cạnh tăng của tín hiệu OUT + (trên phạm vi có nhãn là ‘A> B’), do đó, đây là dạng bắt dạng sóng khi một Điện áp tối đa mới được phát hiện giữa các đầu vào tương tự. Trên thực tế, nó thu được bằng cách xoay một trong các TrimPots của Bảng đánh giá để tăng điện áp tương ứng như trong Hình 22.

Hình 23 cho thấy sơ đồ của Ban Đánh giá.

Phần kết luận

Trong Có thể hướng dẫn này, chúng tôi đã triển khai một công cụ tìm điện áp tối đa (hoặc tối thiểu) tám kênh để được sử dụng như một bổ sung phổ biến cho các hệ thống điều khiển đa kênh. Cách tiếp cận được trình bày khai thác các tính năng nâng cao của các thành phần GreenPAK và chỉ ra cách có thể tích hợp trong một chip duy nhất các chức năng tương tự và kỹ thuật số. Một số IC thương mại có thể được thay thế bằng Dialog GreenPAKs để có thể giảm kích thước và chi phí ứng dụng.

Đề xuất:

Đồng hồ đo điện áp và dòng điện Wifi đa kênh: 11 bước (có hình ảnh)

Đồng hồ đo điện áp và dòng điện Wifi đa kênh: Khi breadboarding, người ta thường cần theo dõi các phần khác nhau của mạch cùng một lúc. Để tránh cảm giác đau đớn khi phải dán các đầu dò vạn năng từ nơi này sang nơi khác, tôi muốn thiết kế một đồng hồ đo dòng điện và điện áp đa kênh. Bo mạch Ina260

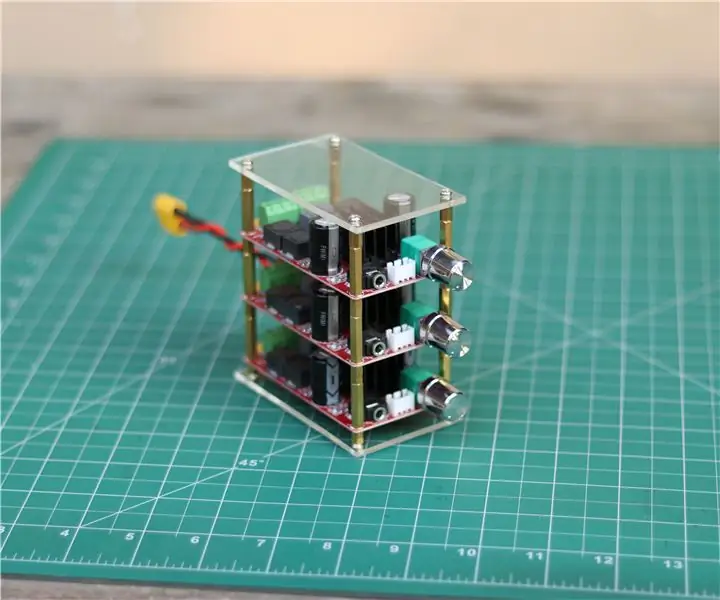

Bộ khuếch đại kênh 5.1 kênh DIY 300 Watt: 12 bước (có hình ảnh)

Bộ khuếch đại 5.1 kênh DIY 300 Watt: Này! Mọi người Tên tôi là Steve. Hôm nay tôi sẽ hướng dẫn các bạn Cách tạo Bộ khuếch đại kênh 5.1. Nhấp vào đây để xem video Hãy bắt đầu

Giới thiệu về điện áp, dòng điện, điện trở và công suất được giải thích cho người mới bắt đầu: 3 bước

Giới thiệu về Điện áp, Dòng điện, Điện trở và Công suất Giải thích cho người mới bắt đầu: Video này liên quan đến các thuật ngữ điện tử cơ bản và dễ hiểu, tôi sẽ cố gắng giải thích dễ dàng bằng khái niệm tương tự nước, vì vậy sẽ giúp hiểu được lý thuyết về bột, vì vậy hãy xem video này để làm rõ khái niệm của bạn về Dòng điện, Điện áp

Làm thế nào để tổ chức một buổi giới thiệu và giới thiệu các tài liệu hướng dẫn: 8 bước

Làm thế nào để tổ chức một buổi trình diễn và kể về những người có thể hướng dẫn: Đây là một hướng dẫn để chạy một Buổi trình diễn và Kể về những người có thể hướng dẫn. Nó chủ yếu dựa trên một sự kiện được tổ chức tại Guiductables vào thứ Sáu, ngày 9 tháng 3 năm 2007, nhưng cũng dựa trên hiện thân trước đó của sự kiện này, Squid Labs Light Salons

Cách làm cho máy tính xách tay của bạn tiết kiệm pin với hiệu suất giảm thiểu tối thiểu: 4 bước

Làm thế nào để máy tính xách tay của bạn tiết kiệm pin với mức giảm hiệu suất tối thiểu: Ai nói rằng máy tính xách tay của bạn phải chịu hiệu suất chậm để tiết kiệm một chút năng lượng? Hiệu suất hoặc tuổi thọ pin của bạn thay đổi như thế nào phụ thuộc vào tuổi máy tính xách tay, tuổi thọ pin cũng như các chương trình và cài đặt khác. Dưới đây là một số bước đơn giản để giúp tăng