Mục lục:

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:36.

- Sửa đổi lần cuối 2025-01-23 15:15.

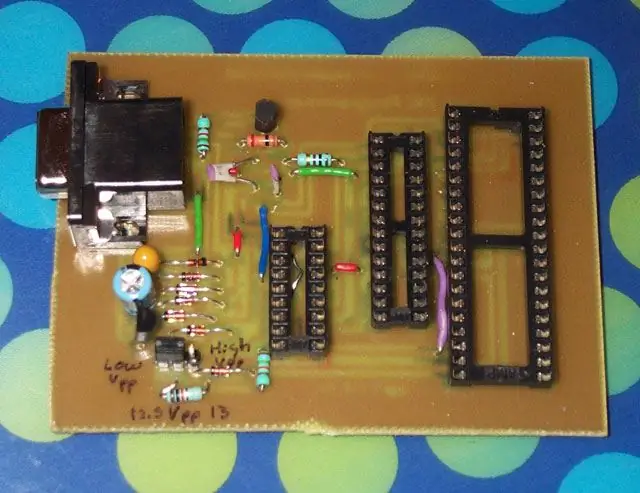

Sơ đồ & bố cục cho một Lập trình PIC JDM2 được cập nhật. Bao gồm bộ lọc đồng hồ & dữ liệu, bộ chia điện áp Vpp cho vi điều khiển PIC hiện đại (ví dụ: USB PIC 18F2455 / 4455). Trước khi đọc các trang web như www.hackaday.com & www.makezine.com/blog Tôi chỉ làm việc với dòng Amtel / AVR của vi điều khiển. Sau khi xem tất cả các dự án thú vị mà mọi người đang làm với PIC của Microchip, tôi XIN LỖI để có một lập trình viên PIC. Khoảng một năm trước, tôi đã tạo lập trình PIC đầu tiên của mình dựa trên thiết kế uJDM (https://www.jdm.homepage.dk/newpic3.htm). Bộ lập trình này sử dụng 6 thành phần chung. Mặc dù liên kết chỉ cho biết '16F84 (a)', tôi đã sử dụng nó cho các bộ xử lý 16F628 (a) hiện đại hơn (và rẻ hơn) mà không gặp vấn đề gì. Lập trình viên này đã phục vụ tôi rất tốt, nhưng nó bị giới hạn ở (ít hơn) PIC 18 chân với Vpp lập trình là 13 vôn. Mạch dựa trên bộ lập trình JDM2 (https://jdm.homepage.dk/newpic.htm), với hai cải tiến: đồng hồ và lọc dòng dữ liệu & điện áp lập trình có thể lựa chọn. Kho lưu trữ ZIP chứa tất cả các tệp dự án. Sơ đồ và bố cục uJDM cũng được bao gồm.

Bước 1: Cải tiến thiết kế

Bộ lọc Đồng hồ và Dữ liệu: Các PIC mới hơn được lập trình nhanh đến mức đồng hồ và các đường dữ liệu có thể trải nghiệm đàm thoại chéo. Theo tác giả của phần mềm lập trình WinPic (https://www.qsl.net/dl4yhf/winpic/): “Có một ghi chú trên diễn đàn Microchip (của Olin Lathrop) về việc lập trình dsPIC30F201, đề nghị đưa 22.. 47 pF trên đường PGD và PGC để nối đất gần chip đích. Ngoài ra, đặt một điện trở 100 ohm nối tiếp với đường PGD giữa chip đích và nắp. Điện trở và nắp trên đường PGD thông thấp lọc tín hiệu PGD khi nó được điều khiển bởi chip đích. Điều này làm giảm các tần số cao có thể ghép vào dòng PGC. Giới hạn trên dòng PGC giúp nó ít bị nhiễu hơn. Sau đó, chúng tôi phát hiện ra rằng lưu ý quan trọng này cũng áp dụng cho dòng PIC18Fxxxx. Một người dùng lập trình Velleman PIC đã báo cáo thành công với PIC18F4520 sau khi thêm các mũ 2 * 33 pF và một điện trở nối tiếp 100 Ohm. " (LINK: https://www.qsl.net/dl4yhf/winpic/#pgd_pgc_filtering) Lưu ý này chủ yếu áp dụng cho lập trình PIC thông qua cáp khi chúng được hàn vào mạch. Khi sử dụng kiểu lập trình này, các tụ điện và điện trở phụ phải ở gần chip mục tiêu - không có ích gì khi có chúng trên lập trình viên: "Điều này có nghĩa là vấn đề này không thể được giải quyết ở đầu cáp của người lập trình. Không có mạch thông minh của lập trình viên có thể giải quyết vấn đề này. Nó phải được xử lý ở mạch đích. (LINK: xem PGD to PGC Crosstalk tại https://www.embedinc.com/picprg/icsp.htm) Tôi nhấn mạnh điều này vì vậy rõ ràng là bạn KHÔNG THỂ đóng tiêu đề ICSP trên bảng này mà không có vấn đề gì. Tôi đã đưa các bộ lọc vào bộ lập trình mới của mình vì các dấu vết dữ liệu / đồng hồ dài. Các tụ điện nằm trong mạch để chúng có thể được loại trừ mà không làm suy yếu dấu vết Điện trở có thể được thay thế bằng dây nhảy. 13 volt. PIC mới hơn (chẳng hạn như USB 18F2455 / 4455 hỗ trợ USB) có mức thấp er Vpp của 12,5 volt. Một bộ chia điện áp đã được thêm vào thiết kế JDM2 để cung cấp 12,5 volt từ đầu ra 13 volt ban đầu. Một diode ngăn chặn sự rò rỉ qua bộ chia điện áp khi nó bị bỏ qua. Vpp có thể được chọn bằng jumper ba chân ở phía dưới bên trái của lập trình viên. Trong thực tế, điều đó dường như không thành vấn đề: Tôi có thể lập trình phần 13 volt với 12,5 volt và phần 12,5 volt ở 13 volt mà không bị hỏng.

Bước 2: Thi công

Các dấu vết trong thiết kế này rất đẹp và béo để dễ dàng chuyển mực (hoặc bảng ảnh lười biếng). Tôi bắt đầu tạo PCB bằng phương pháp TT, nhưng thấy nó khá tẻ nhạt. Khoản đầu tư 10 đô la đã giúp tôi bắt đầu với PCB ảnh (sử dụng các tính năng tích cực về độ trong suốt của tia mực). Tôi sẽ không bao giờ quay trở lại.

Tất cả các bộ phận đều có sẵn tại cửa hàng điện tử địa phương của tôi ở Amsterdam, mặc dù tôi đã đặt hàng số lượng lớn các bộ phận từ Mouser. Mỗi bảng có giá khoảng 2,50 đô la để làm - chi phí lớn nhất là đầu nối DB9 9 chân cái (1,60 đô la). Bố cục và BOM ở bên dưới. Các tệp sơ đồ và bảng dành cho EagleCad. Đừng quên 8 jumper, được hiển thị bằng màu đỏ. Giá trị một phần C1 100uF / 25V C2 22u / 16V Tantal C3 22… 47… 100pf C4 22… 47… 100pf D1 1N4148 D2 5V1 Zener D3 1N4148 D4 1N4148 D5 1N4148 D6 8V2 Zener D7 1N4148 IC1 DIL18S Q1 IC2 DIL28-3 BC IC3 DBIL40 BC547B R1 10k R2 1k5 R3 100ohm R4 1K R5 15K Đầu cắm chân SV3 (3) X1 Đầu nối 9 chân DB9 cái (F09H)

Bước 3: SỬ DỤNG

Lập trình viên sẽ làm việc với bất kỳ phần mềm lập trình nào hỗ trợ JDM2. Tôi thích WinPic800 (LINK: https://perso.wanadoo.es/siscobf/winpic800.htm) và WinPIC cũng xứng đáng được ghi nhận cho thông tin hỗ trợ kỹ thuật tuyệt vời (LINK: https://www.qsl.net/dl4yhf/winpic /). Cả hai đều hỗ trợ USB PIC mới nhất (18F2 / 4455). ICProg rất tuyệt, nhưng chưa được cập nhật trong một thời gian (LINK: https://www.ic-prog.com/). Lập trình viên này đã được thử nghiệm với các PIC sau: Pins Part # 8 12F68314 16F68418 16F84 (a) *, 16F628 (a) * 28 16F737, 18F245540 16F74, 18F4455 * Bản sửa đổi gốc và 'A' OK. Vị trí cho các PIC khác nhau được hiển thị trong sơ đồ bên dưới. Nó không giới hạn ở những PIC này - nó sẽ hoạt động với bất kỳ PIC nào có sắp xếp Vpp, Vss, Vdd, PGD, & PGC như được minh họa.

Bước 4: Cải tiến trong tương lai

Tôi đã sử dụng ổ cắm IC AMP giá rẻ từ Mouser vì tôi đã có chúng trong tay. Thiết kế tiếp theo của tôi sẽ thay thế các ổ cắm 28 và 40 chân bằng một ổ cắm ZIF 40 chân. Một khoảng trống bổ sung xung quanh ổ cắm 18 chân cũng có thể thay thế ZIF.

-ian (hướng dẫn-at-whereisian-dot-com)

Đề xuất:

(gần như) Lập trình viên MIDI SysEx CC đa năng (và Trình tự lập trình tự ): 7 bước (có Hình ảnh)

(gần như) Lập trình viên MIDI SysEx CC đa năng (và Trình lập trình …): Vào giữa những năm tám mươi, các bộ sản xuất tổng hợp bắt đầu " ít hơn là tốt hơn " quá trình dẫn đến synths barebone. Điều này cho phép giảm chi phí về mặt sản xuất, nhưng làm cho quá trình vá lỗi trở nên thành công nếu không muốn nói là không thể sử dụng cuối cùng

Trình tạo nhạc dựa trên thời tiết (Trình tạo âm trung dựa trên ESP8266): 4 bước (có hình ảnh)

Trình tạo nhạc dựa trên thời tiết (Trình tạo âm trung dựa trên ESP8266): Xin chào, hôm nay tôi sẽ giải thích cách tạo trình tạo nhạc dựa trên thời tiết nhỏ của riêng bạn. Nó dựa trên ESP8266, giống như Arduino và nó phản ứng với nhiệt độ, mưa và cường độ ánh sáng. Đừng mong đợi nó có thể tạo ra toàn bộ bài hát hoặc hợp âm

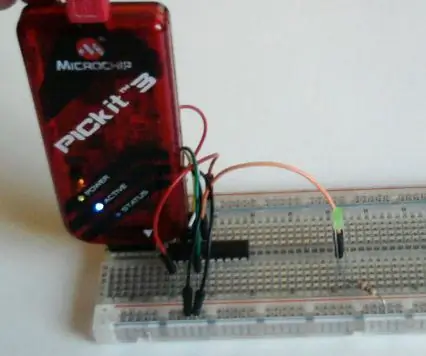

Cách lập trình MCU PIC với bộ lập trình PICkit bằng bảng mạch: 3 bước

Cách lập trình PIC MCU Với Bộ lập trình PICkit Sử dụng Bảng mạch: Bạn không cần các công cụ đắt tiền và phức tạp để chơi với các bộ vi điều khiển PIC (hoặc bất kỳ loại nào khác). Tất cả những gì bạn cần là một bảng mạch để bạn kiểm tra mạch và lập trình của mình. Tất nhiên một số loại lập trình viên và IDE là cần thiết. Trong hướng dẫn này

Pic 16F676 Ổ cắm lập trình ICSP cho Bộ lập trình PICkit 2: 6 bước

Pic 16F676 Ổ cắm lập trình ICSP cho người lập trình PICkit 2: Tôi đang cố gắng xây dựng mô-đun động cơ DC kép này cho dự án rô bốt của mình Và tôi không có không gian để đặt tiêu đề chân ICSP trên PCB. Vì vậy, tôi nhanh chóng chế nhạo thiết kế này

Hướng dẫn lập trình thú vị cho nhà thiết kế - Kiểm soát quy trình chương trình- Tuyên bố vòng lặp: 8 bước

Hướng dẫn lập trình thú vị cho nhà thiết kế - Điều khiển quy trình chương trình- Tuyên bố vòng lặp: Điều khiển quy trình chương trình- Tuyên bố vòng lặp Từ chương này, bạn sẽ tiếp xúc với một điểm kiến thức quan trọng và mạnh mẽ - Câu lệnh vòng lặp. Trước khi đọc chương này, nếu bạn muốn vẽ 10.000 vòng tròn trong chương trình, bạn chỉ có thể thực hiện với một