Mục lục:

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:32.

- Sửa đổi lần cuối 2025-01-23 15:15.

Tôi bị choáng ngợp bởi loại phản hồi mà tôi nhận được trong blog này. Cảm ơn mọi người đã ghé thăm blog của tôi và thúc đẩy tôi chia sẻ kiến thức của mình với các bạn. Lần này, tôi sẽ trình bày thiết kế của một mô-đun thú vị khác mà chúng ta thấy trong tất cả các SOC - Bộ điều khiển ngắt.

Chúng tôi sẽ thiết kế một Bộ điều khiển ngắt lập trình đơn giản nhưng mạnh mẽ. Đây là một thiết kế hoàn toàn có thể định cấu hình và tham số, có thể di động trên các nền tảng. Tôi thiết kế cái này sau khi đọc rất nhiều về một số kiến trúc bộ điều khiển ngắt phổ biến hiện có như NVIC, 8259a, RISC-V PLIC, Microblaze's INTC, v.v. Hy vọng các bạn thấy blog này hữu ích và giúp bạn tìm hiểu cách xử lý ngắt của bộ xử lý với sự trợ giúp của Bộ điều khiển ngắt.

Bước 1: Thông số kỹ thuật

Sau đây là các thông số kỹ thuật của IP:

- Giao diện AHB3-Lite.

-

Các thông số có thể định cấu hình tĩnh:

- Số nguồn ngắt bên ngoài; hỗ trợ lên đến 63 ngắt.

- Số mức độ ưu tiên; hỗ trợ lên đến 63 cấp độ.

- Số cấp độ làm tổ; hỗ trợ lên đến 8 cấp độ làm tổ.

- Chiều rộng xe buýt; 32 hoặc 64.

- Các ngắt có thể che được trên toàn cầu và cục bộ.

- Mức độ ưu tiên có thể cấu hình động cho mỗi ngắt.

- Hai chế độ hoạt động - Chế độ hoàn toàn lồng nhau và Chế độ ưu tiên ngang nhau.

- Hỗ trợ ngắt nhạy ở mức cao đang hoạt động.

Thông số kỹ thuật RISC-V PLIC lấy cảm hứng từ cơ chế bắt tay ngắt được sử dụng trong thiết kế.

Tính năng sẵn sàng ngắt quãng được lấy cảm hứng từ 8259a

Các bài đọc khác: Microblaze INTC, NVIC

Bước 2: Tổng quan về PIC

Bộ điều khiển ngắt lập trình (PIC) nhận nhiều ngắt từ các thiết bị ngoại vi bên ngoài và kết hợp chúng thành một đầu ra ngắt duy nhất đến lõi bộ xử lý đích.

PIC được điều khiển thông qua các thanh ghi điều khiển và trạng thái. Tất cả các thanh ghi PIC đều được ánh xạ bộ nhớ và được truy cập thông qua giao diện bus AHB3-Lite.

Ngân hàng thanh ghi bao gồm thanh ghi cấu hình, thanh ghi cho phép, thanh ghi đang chờ xử lý, thanh ghi trong dịch vụ, thanh ghi ưu tiên và thanh ghi ID, điển hình trong Bộ điều khiển ngắt.

Thanh ghi cấu hình được sử dụng để thiết lập chế độ hoạt động của PIC. Nó có thể hoạt động ở Chế độ lồng nhau hoàn toàn hoặc Chế độ ưu tiên ngang nhau.

Mỗi ngắt có thể được gán mức độ ưu tiên và được che riêng. Mặt nạ toàn cầu của tất cả các ngắt cũng được hỗ trợ.

Ngân hàng đăng ký tương tác với Bộ phân giải ưu tiên và BTC (Bộ phân tích cây nhị phân) để giải quyết mức độ ưu tiên của các ngắt đang chờ xử lý và xác nhận ngắt tới bộ xử lý cho phù hợp. Thanh ghi ID chứa ID của ngắt đang chờ có mức ưu tiên cao nhất.

Bước 3: Thiết kế và triển khai RTL

Thiết kế của PIC nhấn mạnh vào việc giảm độ trễ của việc giải quyết các ưu tiên, đây là phần quan trọng nhất về mặt thời gian của thiết kế. Vì thiết kế giải quyết các ưu tiên trong một chu kỳ xung nhịp duy nhất, hiệu suất giảm khi số lượng nguồn tăng với độ phức tạp Log2.

Thiết kế đã được thực hiện thành công và xác minh thời gian theo tần số trên FPGA Artix-7.

- Lên đến 15 nguồn: 100 MHz

- Lên đến 63 nguồn: 50 MHz

Độ trễ ngắt do PIC thêm vào là 3 chu kỳ đồng hồ (Không bao gồm thời gian chuyển đổi ngữ cảnh của Bộ xử lý và thời gian tìm nạp lệnh ISR đầu tiên).

Bước 4: Ghi chú quan trọng và tệp đính kèm

Lưu ý quan trọng:

- Nếu giao diện AHB3-Lite không mong muốn, bạn có thể thay đổi mô-đun trên cùng và sử dụng thiết kế khung của PIC. Tuy nhiên, băng kiểm tra được cung cấp là dành cho IP với Giao diện AHB3-Lite.

- PIC IP v1.0 là một thiết kế RTL hoàn toàn di động, trần trụi.

- Đã được xác minh chức năng để hoạt động trên cả hai chế độ.

File đính kèm:

- Thiết kế mã và bàn kiểm tra trong VHDL.

- Tài liệu IP đầy đủ.

Nó là một thiết kế mã nguồn mở… Hãy thoải mái sử dụng…

Đối với bất kỳ câu hỏi nào, bất kỳ lúc nào:

Mitu Raj

Đề xuất:

Lập trình vi điều khiển với bộ lập trình USBasp trong Atmel Studio: 7 bước

Lập trình vi điều khiển với một lập trình viên USBasp trong Atmel Studio: Hi Tôi đã đọc và học qua nhiều hướng dẫn dạy cách sử dụng lập trình USBasp với Arduino IDE, nhưng tôi cần sử dụng Atmel Studio để làm bài tập ở trường Đại học và không thể tìm thấy bất kỳ hướng dẫn nào. Sau khi nghiên cứu và đọc qua nhiều r

ESP8266 RGB LED STRIP Điều khiển WIFI - NODEMCU làm điều khiển từ xa hồng ngoại cho dải đèn Led được điều khiển qua Wi-Fi - Điều khiển điện thoại thông minh RGB LED STRIP: 4 bước

ESP8266 RGB LED STRIP Điều khiển WIFI | NODEMCU làm điều khiển từ xa hồng ngoại cho dải đèn Led được điều khiển qua Wi-Fi | Điều khiển bằng điện thoại thông minh RGB LED STRIP: Xin chào các bạn trong hướng dẫn này, chúng ta sẽ học cách sử dụng gật đầu hoặc esp8266 làm điều khiển từ xa IR để điều khiển dải LED RGB và Nodemcu sẽ được điều khiển bằng điện thoại thông minh qua wifi. Vì vậy, về cơ bản bạn có thể điều khiển DÂY CHUYỀN LED RGB bằng điện thoại thông minh của mình

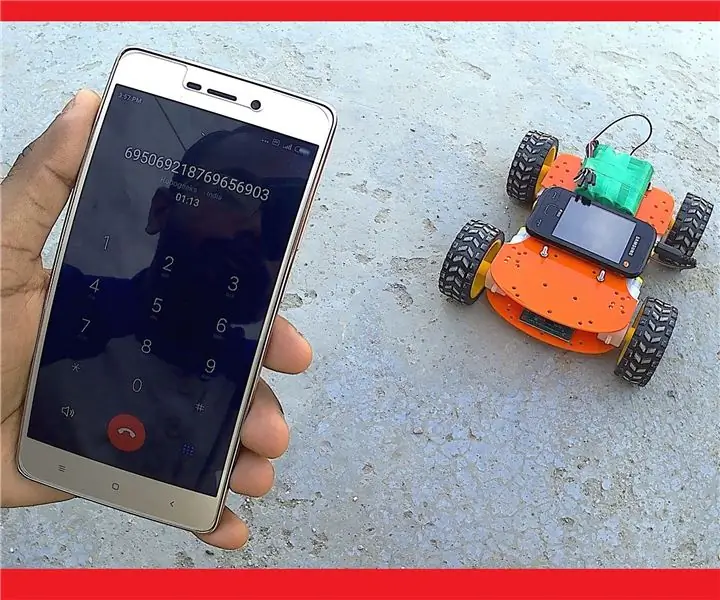

Cách chế tạo Robot điều khiển di động - Dựa trên DTMF - Không có Vi điều khiển & Lập trình - Kiểm soát từ mọi nơi trên thế giới - RoboGeeks: 15 bước

Cách chế tạo Robot điều khiển di động | Dựa trên DTMF | Không có Vi điều khiển & Lập trình | Kiểm soát từ mọi nơi trên thế giới | RoboGeeks: Muốn tạo ra một robot có thể được điều khiển từ mọi nơi trên thế giới, Hãy làm điều đó

Điều khiển các thiết bị điện của bạn bằng Điều khiển từ xa Tv (Điều khiển từ xa) với Màn hình nhiệt độ và độ ẩm: 9 bước

Điều khiển thiết bị điện của bạn bằng Điều khiển từ xa Tv (Điều khiển từ xa) Có Hiển thị nhiệt độ và độ ẩm: xin chào, tôi là Abhay và đây là blog đầu tiên của tôi về Các thiết bị điện và hôm nay tôi sẽ hướng dẫn bạn cách điều khiển các thiết bị điện bằng điều khiển từ xa bằng cách xây dựng cái này dự án đơn giản. cảm ơn atl lab đã hỗ trợ và cung cấp tài liệu

Hướng dẫn lập trình thú vị cho nhà thiết kế - Kiểm soát quy trình chương trình- Tuyên bố vòng lặp: 8 bước

Hướng dẫn lập trình thú vị cho nhà thiết kế - Điều khiển quy trình chương trình- Tuyên bố vòng lặp: Điều khiển quy trình chương trình- Tuyên bố vòng lặp Từ chương này, bạn sẽ tiếp xúc với một điểm kiến thức quan trọng và mạnh mẽ - Câu lệnh vòng lặp. Trước khi đọc chương này, nếu bạn muốn vẽ 10.000 vòng tròn trong chương trình, bạn chỉ có thể thực hiện với một