Mục lục:

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:36.

- Sửa đổi lần cuối 2025-01-23 15:15.

Đây là hướng dẫn về cách tạo đồng hồ bấm giờ một phút bằng VHDL và bảng Basys 3. Một thiết bị như vậy là lý tưởng cho các trò chơi mà mỗi người chơi có tối đa một phút để di chuyển. Đồng hồ bấm giờ hiển thị chính xác giây và mili giây trên màn hình bảy phân đoạn, bắt đầu từ 0 giây và 0 mili giây, lên đến 60 giây và 0 mili giây. Hai nút cũng được sử dụng: nút trung tâm, được sử dụng để bắt đầu, dừng và tiếp tục bộ đếm thời gian, và nút bên phải, được sử dụng để khởi động lại bộ hẹn giờ. Khi thiết bị được so sánh cạnh nhau với đồng hồ bấm giờ tích hợp của điện thoại thông minh, độ chính xác của đồng hồ là đáng chú ý.

Bước 1: Lấy phần cứng / phần mềm

1. Bảng đào tạo Basys 3 Artix-7 FPGA của Digilent với Cáp Micro-USB sang USB

2. Vivado 2016.2 Design Suite từ Xilinx

Bước 2: Sơ đồ khối

Mạch này được xây dựng theo hành vi và sử dụng các thành phần Xilinx tích hợp sẵn, nhưng cũng có thể được mô tả về mặt cấu trúc, như thể hiện bằng sơ đồ cấu trúc chung ở trên. Từ sơ đồ, có thể thấy rằng mạch được điều khiển bởi hai bộ phân tần. Một trong các bộ phân tần chạy ở tốc độ 1 centi giây và điều khiển bộ đếm cực âm được sử dụng làm các số hiển thị trên màn hình bảy đoạn. Bộ phân tần thứ hai chạy ở 240Hz và được sử dụng để điều khiển bộ đếm cực dương quay qua các cực dương để tất cả các số hiển thị chính xác trên màn hình bảy đoạn. Bộ mã hóa lấy logic cathode từ bộ đếm cathode và logic anode từ bộ đếm anode và mã hóa nó đến cực âm và cực dương của đầu ra chạy màn hình bảy đoạn. Chức năng của bộ mã hóa này là cho đầu ra cực âm thay đổi mỗi khi đầu ra cực dương thay đổi. Đầu ra catốt không thể chạy độc lập với bộ đếm vì các cực dương phải quay qua 4 chữ số riêng biệt.

Bước 3: Mô-đun dự án

Đầu tiên, một khối quá trình cho CEN được tạo ra để khi phát hiện một nút nhấn, BẬT sẽ chuyển đổi. Điều này đóng vai trò là điểm dừng / bắt đầu của bộ đếm cực âm.

Trong khối xử lý tiếp theo, các tín hiệu xung nhịp centisecond và 240Hz được thiết lập để các bộ đếm tương ứng của chúng tăng lên 1 mỗi khi xung nhịp 100mHz bên trong đạt đến một cạnh tăng. Khi bộ đếm centisecond đạt đến 500000, nó sẽ đặt lại về 0. Trong khi đó, bộ đếm 240Hz sẽ đặt lại khi số đếm đạt đến 41667.

Đối với phần cathode của mã, nếu ENABLE là "0" thì việc đếm cathode sẽ tạm dừng. Nếu nút đặt lại được nhấn trong thời gian này, thì tất cả số đếm được đặt lại thành "0000". Trong khi đó, nếu ENABLE là '1', việc đếm catốt sẽ tiếp tục cho đến khi số lượng catốt đạt đến 60,00, trong đó nó kích hoạt tín hiệu dừng là '1'. Tín hiệu dừng quay trở lại khối xử lý CEN và khiến ENABLE là "0" trong khi tín hiệu dừng là "1" và sẽ không thay đổi cho đến khi nhấn nút đặt lại.

Cuối cùng, màn hình bảy đoạn được thiết lập bằng cách kết nối chính xác 4 cực dương với mỗi 8 cực âm của chúng để hiển thị đồng thời các chữ số tương ứng 0-9 của chúng.

Bước 4: Ràng buộc

Tệp ràng buộc này kết nối các đầu vào và đầu ra được chỉ định từ VHDL vào các bộ phận vật lý, cần thiết của bảng Basys. Đối với dự án này, các thành phần bao gồm bốn cực dương và mỗi cực âm trong số tám cực âm của chúng cho màn hình bảy phân đoạn, đồng hồ 100 mHz bên trong, nút trung tâm và nút bên phải.

Bước 5: Kiểm tra

Khi bạn đã hoàn thành mã, bây giờ bạn có thể lập trình FPGA qua cáp USB. Màn hình bảy phân đoạn sẽ hiển thị 0,00. Kiểm tra xem các nút có hoạt động hay không bằng cách nhấn vào nút trung tâm để bắt đầu hẹn giờ cho đến khi đạt 60.00 và dừng lại; bất cứ lúc nào ở giữa, bạn có thể nhấn lại nút trung tâm để tạm dừng. Khi nó bị tạm dừng, bạn có thể nhấn nút bên phải để đặt lại bộ hẹn giờ về 0,00. Nếu mọi thứ hoạt động bình thường, xin chúc mừng bạn vừa tạo được bộ đếm thời gian một phút!

Đề xuất:

Động cơ bước Điều khiển động cơ bước Động cơ bước - Động cơ bước như một bộ mã hóa quay: 11 bước (có hình ảnh)

Động cơ bước Điều khiển động cơ bước Động cơ bước | Động cơ bước như một bộ mã hóa quay: Có một vài động cơ bước nằm xung quanh và muốn làm điều gì đó? Trong Có thể hướng dẫn này, hãy sử dụng động cơ bước làm bộ mã hóa quay để điều khiển vị trí của động cơ bước khác bằng vi điều khiển Arduino. Vì vậy, không cần phải quảng cáo thêm, chúng ta hãy

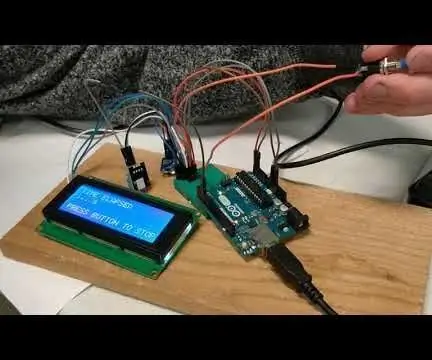

Đồng hồ bấm giờ tự động: 9 bước

Đồng hồ bấm giờ tự động: Có thể hướng dẫn này sẽ chỉ cho bạn cách chế tạo đồng hồ bấm giờ tự động. Bởi vì chạy bộ là một niềm vui, nhưng đôi khi bạn không có bất kỳ ai có thể dành thời gian cho bạn. Tôi đã cố gắng giữ cho nó đơn giản, rẻ và chính xác nhất có thể. Bạn không cần điều khiển từ xa

Đồng hồ bấm giờ cơ bản sử dụng VHDL và Bảng Basys3: 9 bước

Đồng hồ bấm giờ cơ bản sử dụng bảng VHDL và Basys3: Chào mừng bạn đến với tài liệu hướng dẫn về cách tạo đồng hồ bấm giờ bằng bảng VHDL và Basys 3 cơ bản. Chúng tôi rất vui mừng được chia sẻ dự án của chúng tôi với bạn! Đây là dự án cuối cùng cho khóa học CPE 133 (Thiết kế kỹ thuật số) tại Cal Poly, SLO vào mùa Thu năm 2016. Dự án chúng tôi xây dựng

Đồng hồ Arduino / Đồng hồ bấm giờ đơn giản: 6 bước (có hình ảnh)

Đồng hồ Arduino / Đồng hồ bấm giờ đơn giản: Cái này " có thể hướng dẫn " sẽ chỉ và hướng dẫn bạn cách tạo một chiếc đồng hồ Arduino Uno đơn giản cũng hoạt động như một chiếc đồng hồ bấm giờ chỉ trong một vài bước đơn giản

Đồng hồ bấm giờ VHDL: 8 bước (có hình ảnh)

Đồng hồ bấm giờ VHDL: Đây là hướng dẫn về cách tạo đồng hồ bấm giờ bằng VHDL và bảng mạch FPGA, như Bảng Basys3 Atrix-7. Đồng hồ bấm giờ có thể đếm từ 00,00 giây đến 99,99 giây. Nó sử dụng hai nút, một cho nút khởi động / dừng và một cho