Mục lục:

- Bước 1: Xây dựng Mô-đun PWM- Tệp nguồn

- Bước 2: Xây dựng Mô-đun PWM- Thiết lập Vivado

- Bước 3: Xây dựng mô-đun PWM- Tạo tệp dự án

- Bước 4: Xây dựng mô-đun PWM- Thiết kế khối và cài đặt tệp ràng buộc (I)

- Bước 5: Xây dựng mô-đun PWM- Thiết kế khối và cài đặt tệp ràng buộc (II)

- Bước 6: Xây dựng mô-đun PWM- Thiết kế khối và cài đặt tệp ràng buộc (III)

- Bước 7: Xây dựng mô-đun PWM- Thiết kế khối và cài đặt tệp ràng buộc (IV)

- Bước 8: Xây dựng mô-đun PWM- Thiết kế khối và cài đặt tệp ràng buộc (V)

- Bước 9: Xây dựng mô-đun PWM- Cài đặt phần cứng

- Bước 10: Xây dựng mô-đun PWM- Tạo luồng bit và khởi chạy SDK

- Bước 11: Xây dựng mô-đun PWM- Tạo ứng dụng mới trong Xilinx SDK

- Bước 12: Xây dựng Mô-đun PWM- Tổng quan về Trình khám phá dự án (I)

- Bước 13: Xây dựng Mô-đun PWM- Tổng quan về Trình khám phá dự án (II)

- Bước 14: Xây dựng Mô-đun PWM- Tổng quan về Trình khám phá dự án (III)

- Bước 15: Xây dựng mô-đun PWM- Kết thúc chức năng PWM (I)

- Bước 16: Xây dựng mô-đun PWM- Kết hợp chức năng PWM (II)

- Bước 17: Xây dựng mô-đun PWM- Kết hợp chức năng PWM (III)

- Bước 18: Xây dựng Mô-đun PWM- Chạy ngay

- Bước 19: Xử lý video trực tuyến trên Digilent ZYBO với OV7670

- Bước 20: Hoàn thành sơ đồ khối

- Bước 21: Kết nối OV7670 với ZYBO

- Bước 22: Tạo thiết kế khối

- Bước 23: Thêm tệp VHDL để điều khiển và chụp camera OV7670

- Bước 24: Thêm tệp ràng buộc

- Bước 25: Thêm IP Repo cho HLS IP

- Bước 26: Thêm mô-đun và IP

- Bước 27: Cài đặt cấu hình IP

- Bước 28: Thêm và cấu hình PS IP Block

- Bước 29: Phần 1. Xây dựng Mô-đun PWM cho Động cơ Servo

- Bước 30: Kết nối phía đầu vào video (đánh dấu aclk)

- Bước 31: Kết nối với OV7670

- Bước 32: Kết nối trên Video Out Side

- Bước 33: Chạy tự động hóa khối và kết nối

- Bước 34: Tạo HDL Wrapper

- Bước 35: Tạo Bitstream, Xuất phần cứng sang SDK, Khởi chạy SDK từ Vivado

- Bước 36: SDK (không có FreeRTOS)

- Bước 37: Triển khai FreeRTOS

- Bước 38: Hướng dẫn sử dụng

- Bước 39: Tham khảo và liên kết

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:35.

- Sửa đổi lần cuối 2025-01-23 15:15.

Bắt đầu ở bước một để biết chi tiết về cách tạo bộ điều khiển PWM servo 2 trục.

Bắt đầu từ sơ đồ khối lớn (Bước 19) cho toàn bộ dự án.

Thiết lập máy ảnh + xoay / nghiêng mà chúng tôi đã sử dụng:

PmodCON3 từ Digilent được sử dụng để kết nối các servos.

Bước 1: Xây dựng Mô-đun PWM- Tệp nguồn

Bước 2: Xây dựng Mô-đun PWM- Thiết lập Vivado

Đầu tiên, hãy tải xuống trang web Vivado Design Suite From Xilinx. Cài đặt tất cả bộ thiết kế, bao gồm Bộ phát triển phần mềm Vivado (SDK). Dự án này sử dụng phiên bản 2017.2.

Đồng thời, Digilent Adept 2 cũng nên được cài đặt làm trình điều khiển bo mạch Zybo.

Bước 3: Xây dựng mô-đun PWM- Tạo tệp dự án

Trước khi tạo tệp dự án, bạn nên đảm bảo rằng bạn đã cài đặt tệp Zybo đúng cách như hướng dẫn ở đây:

Phiên bản Vivado 2015.1 và Cài đặt tệp bảng sau

Mở Vivado 2017.2. Trên Quick Start, nhấp vào Create Project -> Next -> Project Name (Đặt tên dự án của bạn ở đây) -> Loại dự án. Trên Loại dự án, chọn Dự án RTL và đánh dấu vào “Không chỉ định nguồn tại thời điểm này”. Tiếp theo, đối với Phần mặc định, chọn “Bo mạch” và “Zybo” làm Tên hiển thị. Tiếp theo, Click vào Finish để bắt đầu dự án.

Bước 4: Xây dựng mô-đun PWM- Thiết kế khối và cài đặt tệp ràng buộc (I)

Trên Flow Navigator, nhấp vào “” Create Block Design”, sau đó nhấn OK. nhấp vào dấu “+” để thêm các IP cần thiết. Thêm vào:

- Một hệ thống xử lý ZYNQ7 Hai bộ hẹn giờ AXI

- Hai bộ hẹn giờ AXI

Bước 5: Xây dựng mô-đun PWM- Thiết kế khối và cài đặt tệp ràng buộc (II)

Sau khi Thêm IP, hãy chạy Tự động hóa khối và tự động hóa kết nối. Sau khi quá trình tự động hóa hoàn tất, trên khối “axi_timer_0”, nhấp chuột phải vào pwm0 -> Tạo bên ngoài. Đặt tên cho chân ngoài pwm0 là pwm_Xaxis. Ngoài ra, lặp lại quá trình trên trên khối “axi_timer_1” và đặt tên cho chân ngoài pwm0 là pwm_Zaxis.

Bước 6: Xây dựng mô-đun PWM- Thiết kế khối và cài đặt tệp ràng buộc (III)

Lưu ý rằng mỗi khi hoàn thành Thiết kế khối trong Vivado, chúng ta cần tạo HDL Wrapper. Vì nó sẽ là mô-đun cấp cao nhất cho mỗi dự án.

Bước 7: Xây dựng mô-đun PWM- Thiết kế khối và cài đặt tệp ràng buộc (IV)

Bây giờ, chúng ta cần thiết lập tệp ràng buộc của mình để gán các chân kết nối với sơ đồ khối của chúng ta. Đóng cửa sổ Thiết kế khối, tab Trên nguồn, “Thêm nguồn” -> Thêm hoặc tạo ràng buộc-> thêm Zybo-Master.xdc làm tệp ràng buộc của chúng tôi.

Bước 8: Xây dựng mô-đun PWM- Thiết kế khối và cài đặt tệp ràng buộc (V)

Mở tệp ràng buộc Zybo-Master.xdc từ thư mục Constraints, bỏ ghi chú các cổng mà chúng tôi muốn chỉ định làm tín hiệu đầu ra và đổi tên “get_ports {XXXX}”, XXXX biểu thị chân bên ngoài có tên trong Sơ đồ khối. Thiết lập của tệp ràng buộc được hiển thị trong hình.

Bước 9: Xây dựng mô-đun PWM- Cài đặt phần cứng

Kết nối động cơ servo với Pmod CON3. TowerPro SG90 là mô hình động cơ servo mà chúng tôi sử dụng trong dự án này. Đối với dây động cơ servo, dây màu cam đại diện cho tín hiệu PWM, được kết nối với chân SIG trong Pmod CON3. Dây màu đỏ Vcc là dây nguồn được kết nối với chân VS trong Pmod CON3. Cuối cùng, dây màu nâu Gnd là dây nối đất nối với chân GND. Tiếp theo, chèn Pmod CON3 vào hàng trên của cổng JD trong Bảng Zybo.

Bước 10: Xây dựng mô-đun PWM- Tạo luồng bit và khởi chạy SDK

1. trong tab Project Navigator, chạy Generate BitStream.

2. Xuất phần cứng: File> Export> Export Hardware-> đánh dấu vào “include bitstream” -> OK 3. Launch SDK: File -> Launch SDK.

Bước 11: Xây dựng mô-đun PWM- Tạo ứng dụng mới trong Xilinx SDK

Tạo một ứng dụng mới:

Tệp> Mới> Dự án ứng dụng -> Nhập tên dự án của bạn -> Kết thúc

Trong Project Explorer, sẽ có ba thư mục.

Trong trường hợp này, “design_1_wrapper_hw_platform_0” là thư mục được Vivado xuất trước đó. Axis_2_PWM_SDK_bsp là thư mục gói hỗ trợ hội đồng quản trị. Và Axis_2_PWM_SDK là thư mục dự án chính của chúng tôi trong SDK. Bạn có thể thấy tệp “helloworld.c” trong thư mục “src” của Axis_2_PWM_SDK, trong đó “helloworld.c” là tệp chính.

Bước 12: Xây dựng Mô-đun PWM- Tổng quan về Trình khám phá dự án (I)

Hãy kiểm tra một số tệp trong Project Explorer. Đầu tiên, trong thư mục “design_1_wrapper_hw_platform_0”, hãy mở “system.hdf”. Tệp này minh họa bản đồ địa chỉ cho bộ xử lý ps7_cortex9 và các khối IP có trong thiết kế của chúng tôi.

Bước 13: Xây dựng Mô-đun PWM- Tổng quan về Trình khám phá dự án (II)

Sau đó, kiểm tra tệp “include” và “libsrc” trong thư mục “Axis_2_PWM_SDK_bsp”. Các tệp thư viện ở đây cho phép chúng tôi tương tác với các thiết bị ngoại vi phần cứng mà không cần đăng ký "chơi".

Bước 14: Xây dựng Mô-đun PWM- Tổng quan về Trình khám phá dự án (III)

Thông qua tài liệu BSP, xtmrctr.h được tìm thấy như một Thư viện điều khiển bộ hẹn giờ Xilinx liên quan đến Bộ hẹn giờ AXI. Thông thường, chúng ta có thể tìm thấy hàm PWM mong muốn ở đây. Tuy nhiên, nếu bạn đọc tài liệu “tmrctr_v4_3”, điều đó cho thấy rằng trình điều khiển hiện không hỗ trợ hoạt động PWM của thiết bị. Do thiếu chức năng PWM, chúng tôi phải hoàn thiện chức năng PWM của mình với sự hỗ trợ của xtmrctr.h và AXI Timer v2.0 LogiCORE IP Product Guide.

Bước 15: Xây dựng mô-đun PWM- Kết thúc chức năng PWM (I)

Quay lại tệp chính “helloworld.c”, bao gồm các tệp tiêu đề sau:

Bước 16: Xây dựng mô-đun PWM- Kết hợp chức năng PWM (II)

Xác định địa chỉ cơ sở của hai AXI TImer thông qua “xparameters.h”.

Bước 17: Xây dựng mô-đun PWM- Kết hợp chức năng PWM (III)

Xây dựng chức năng PWM mong muốn.

Duty_val: chuyển đổi giá trị độ thành chu kỳ nhiệm vụ. PWM_Freq_Duty: đặt tần số và chu kỳ nhiệm vụ mong muốn để tạo ra PWM. Khoảng thời gian đồng hồ cũng nên được chỉ định.

PWM_START: gán địa chỉ thanh ghi PWM và bắt đầu tạo PWM.

PWM_STOP: gán địa chỉ thanh ghi PWM và ngừng tạo PWM.

Phần còn lại của mã demo được hiển thị trong “helloworld.c” trong “Axis_2_PWM_SDK”

Bước 18: Xây dựng Mô-đun PWM- Chạy ngay

1. Lập trình FPGA thông qua SDK

- Kết nối Zybo Board thông qua cổng USB với PC.

- Công cụ Xilinx -> Chương trình FPGA

2. chạy chương trình

Nhấp vào biểu tượng “Run” và thả xuống menu -> Run As -> Khởi chạy trên phần cứng

3. Thiết bị đầu cuối SDK

- Mở SDK Terminal -> Kết nối với Cổng nối tiếp -> OK

- Chạy chương trình. Nếu mã demo chạy thành công, bạn sẽ thấy thông báo “Đã khởi tạo xong!” trên SDK Terminal.

Bước 19: Xử lý video trực tuyến trên Digilent ZYBO với OV7670

Tệp lưu trữ hoàn chỉnh đính kèm.

Bước 20: Hoàn thành sơ đồ khối

Điều này cho thấy sơ đồ hoàn chỉnh của tất cả các kết nối và khối IP trong dự án

Bước 21: Kết nối OV7670 với ZYBO

Tạo kết nối để nối mô-đun ov7670 với ZYBO Pmods

Pmod dữ liệu là Pmod D

Pmod điều khiển là Pmod C

Ngoài ra, hãy kết nối PmodCON3 và servos như được chỉ định trong nửa đầu của hướng dẫn này

Bước 22: Tạo thiết kế khối

Trong Flow Navigator, nhấp vào "Create Block Design", sau đó nhấn OK.

Bước 23: Thêm tệp VHDL để điều khiển và chụp camera OV7670

Thêm các tệp VHDL được đính kèm ở bước này vào dự án

Bước 24: Thêm tệp ràng buộc

Thêm tệp ràng buộc đính kèm vào dự án của bạn.

Bước 25: Thêm IP Repo cho HLS IP

Lấy tệp Zip đính kèm và giải nén nó vào một thư mục mới có tên tương tự trong một thư mục (thư mục) mới có tên "HLS_repo".

Thêm kho lưu trữ IP vào dự án của bạn bằng cách đi tới danh mục IP và nhấp chuột phải chọn "Thêm kho lưu trữ…"

Điều hướng đến thư mục "HLS_repo" của bạn và chọn nó.

Tùy chọn: Tạo khối xử lý video HLS cho chính bạn!

Bước 26: Thêm mô-đun và IP

Thêm các mô-đun ov7670_axi_stream_capture, debounce và ov7670_controller vào sơ đồ khối bằng cách nhấp chuột phải vào nền và chọn "Thêm mô-đun…"

Tương tự, thêm các IP:

- HLS_Video_Track

- Ghi bộ đệm khung hình video

- Đọc bộ đệm khung hình video

- Bộ điều khiển thời gian video

- AXI4-Stream to Video Out

- 3 của "Slice"

- Hằng số

- 2 của Bộ hẹn giờ AXI

Bước 27: Cài đặt cấu hình IP

Như trong hình ảnh

Bước 28: Thêm và cấu hình PS IP Block

Thêm Hệ thống xử lý ZYNQ7 vào sơ đồ khối

chỉnh sửa cấu hình:

-

Cấu hình PS-PL

-

HP

- Bật S HP 0

- Bật S HP 1

-

-

Cấu hình đồng hồ

-

Đồng hồ vải PL

- FCLK_0 ở 100MHz

- FCLK_1 ở 25MHz (OutputClock)

- FLCK_2 ở 35MHz (<= 50MHz) (CameraClock)

-

Bước 29: Phần 1. Xây dựng Mô-đun PWM cho Động cơ Servo

Đưa axi_timer_0 pwm0 ra cổng đầu ra mới pwm_Xaxis

Đưa axi_timer_1 pwm0 ra cổng đầu ra mới pwm_Zaxis

Bước 30: Kết nối phía đầu vào video (đánh dấu aclk)

Kết nối các khối IP phía đầu vào video một cách chính xác

(* các kết nối này nên được tạo bằng cách chọn các tùy chọn phù hợp trong quá trình tự động hóa kết nối) "aclk" từ axi_stream_capture chuyển đến:

- ap_clk trên ghi bộ đệm khung hình video

- ap_clk trên khối xử lý luồng video HLS

- * aclk trên AXI smartconnect IP từ Video Frame Buffer Ghi vào S_AXI_HP0

- * aclk tương ứng với các kênh của IP kết nối AXI cho các kênh S_AXI của khối xử lý video HLS và bộ đệm khung video ghi S_AXI_HP0_ACLK trên khối PS

Tín hiệu luồng video được kết nối đơn giản theo chuỗi từ khối chụp đến giao diện bộ nhớ Zynq.

- Video đi từ khối chụp sang khối xử lý HLS.

- Video được xử lý từ khối HLS chuyển đến khối ghi bộ đệm khung.

- * Khối ghi bộ đệm khung kết nối với giao diện HP0 trên khối Zynq PS.

- Tín hiệu m_axis_tuser từ đầu ra của khối chụp được nối dây thủ công tới cả tín hiệu đầu vào video_in_TUSER trên khối xử lý HLS và tín hiệu ap_start trên cùng một khối.

Tín hiệu TUSER (tuser) được sử dụng bởi giao thức luồng video AXI để chỉ ra thời điểm bắt đầu một khung của video. AP_Start yêu cầu khối HLS bắt đầu xử lý. đi vào. Khi kết nối một tín hiệu của xe buýt và tách nó ra theo cách này, cũng cần phải kết nối nó với điểm kết thúc bình thường của phần còn lại của xe buýt. Vivado giả định rằng nếu bạn đang kết nối tín hiệu theo cách thủ công mà bạn muốn ngắt kết nối tín hiệu thường kết nối.

Cài đặt cấu hình của khối IP:

Ghi bộ đệm khung hình video:

Định dạng video: RGB8

1 mẫu mỗi đồng hồ Số cột tối đa: 1280 (> = 640) Hàng tối đa: 960 (> = 480) Độ rộng dữ liệu tối đa: 8

Bước 31: Kết nối với OV7670

Trên khối ov7670_axi_stream_capture

- Đặt tất cả các đầu vào bên ngoài (nhấp chuột phải vào ghim và chọn từ menu hoặc nhấp chuột trái-> ctrl + T)

- Giữ nguyên tên

Trên khối ov7670_controller

- Đặt tất cả các đầu ra khối bên ngoài

- Đổi tên cổng config_ished thành led0

- kết nối clk với CameraClock (<= 50MHz) (FCLK_2)

Trên khối debounce

- kết nối đầu vào button1 với cổng đầu vào bên ngoài được gọi là btn0

- kết nối out1 với dòng gửi lại trên khối IP ov7670_controller

- kết nối đầu vào button2 với cổng đầu vào bên ngoài được gọi là btn3

- kết nối out2n với đầu vào ext_reset_in trên IP Đặt lại hệ thống bộ xử lý cho miền đồng hồ quay video. (* Điều này có thể cần được thực hiện sau khi IP đó được tạo *)

- kết nối clk với CameraClock (<= 50MHz) (FCLK_2)

Bước 32: Kết nối trên Video Out Side

Kết nối cho các khối Bộ điều khiển thời gian video (VTC), AXI4-Stream to Video Out, và các lát cắt

- Sử dụng xung nhịp 25MHz (FCLK_1) cho vid_io_out_clk và VTC clk

- Sử dụng xung nhịp 100MHz (FCLK_0) cho aclk trên AXI4-Stream to Video Out

- vtiming_out thành vtiming_in

- Video Frame Buffer Read m_axis_video chuyển đến AXI4-Stream to Video Out video_in

- vtg_ce chuyển đến gen_clken

- Buộc VTC clken, aclken, vid_io_out_ce với Constant dout [0: 0]

- Đưa vid_hsync và vid_vsync ra các cổng đầu ra bên ngoài lần lượt là vga_hs và vga_vs. (không có hình)

Lát:

-

Slices phải được thiết lập như trong hình ảnh đính kèm

- đổi tên các khối thành slice_red, slice_green và slice_blue

- thiết lập phạm vi lát cắt như được hiển thị trong hình ảnh theo tên của khối

- kết nối đầu ra từng lát với đầu ra cổng bên ngoài như trong hình.

- vid_data [23: 0] kết nối với đầu vào cho mỗi lát (Din [23: 0])

Bước 33: Chạy tự động hóa khối và kết nối

Chạy Tự động hóa khối để kết nối các thứ từ khối PS ZYNQ7. Như hình minh họa.

Chạy tự động hóa Kết nối để tạo tất cả IP kết nối. Hãy chú ý đến tất cả các tùy chọn trong mỗi hình ảnh.

Trên khối gỡ lỗi, kết nối out2n với miền đồng hồ quay video Bộ xử lý Hệ thống Đặt lại đầu vào ext_reset_in.

Bước 34: Tạo HDL Wrapper

Tạo HDL Wrapper cho thiết kế khối của bạn.

Đặt nó làm mô-đun hàng đầu.

Bước 35: Tạo Bitstream, Xuất phần cứng sang SDK, Khởi chạy SDK từ Vivado

Đảm bảo bao gồm dòng bit khi xuất.

Quá trình tạo dòng bit có thể mất một thời gian rất dài.

Sau đó khởi chạy SDK

Bước 36: SDK (không có FreeRTOS)

Phiên bản này thực hiện mọi thứ mà không cần sử dụng FreeRTOS, cô đọng mã một cách độc đáo.

Tạo một BSP độc lập dựa trên thiết kế phần cứng. Các tùy chọn mặc định sẽ ổn. Đảm bảo rằng các nguồn BSP đã được tạo.

Tạo ứng dụng như trong Hình. (ứng dụng trống)

Xóa main được tạo tự động và nhập các tệp đính kèm.

Bước 37: Triển khai FreeRTOS

Phiên bản này sử dụng FreeRTOS. Tạo một BSP FreeRTOS901 dựa trên thiết kế phần cứng. Các tùy chọn mặc định sẽ ổn. Đảm bảo rằng các nguồn BSP đã được tạo.

Tạo ứng dụng như trong Hình. (ứng dụng trống)

Xóa main được tạo tự động và nhập các tệp đính kèm.

Bước 38: Hướng dẫn sử dụng

Dự án này là một chút khó khăn để chạy. Làm theo các bước theo thứ tự.

Đảm bảo rằng ZYBO của bạn không tự tải bất cứ thứ gì khi được bật nguồn. Điều này có nghĩa là đèn LED Hoàn tất sẽ không sáng. Một cách để làm điều này là đặt jumper nguồn khởi động thành JTAG.

Mở dự án (FreeRTOS hoặc không) mà bạn muốn lập trình từ SDK

- Bật ZYBO của bạn. Đèn LED Hoàn tất sẽ không sáng.

- Lập trình FPGA với tệp bit. Đèn LED Xong sẽ sáng lên. Led0 nên không sáng.

- Chạy mã (hãy nhớ vượt qua điểm ngắt bắt đầu nếu bạn đang làm điều đó).

Tại thời điểm này, bạn sẽ nhận được đầu ra trên màn hình VGA của mình.

Để khởi động lại (nếu lỗi hoặc bất cứ điều gì): chạm nhanh vào nút PS-SRST hoặc tắt ZYBO rồi bật lại. Tiếp tục từ bước 2.

Việc dừng bộ xử lý với trình gỡ lỗi sẽ khiến Máy ảnh giữ nguyên vị trí thay vì di chuyển. Luồng video vẫn sẽ tiếp tục.

Bước 39: Tham khảo và liên kết

Tài liệu hướng dẫn và tài liệu tham khảo Xilinx:

- PG044 - AXI-Stream to Video Out

- PG278 - Đọc / ghi bộ đệm khung hình video

Các liên kết khác:

- Blog của Lauri - đầu vào VDMA

- Blog của Lauri - Đầu ra OV7670 sang VGA sử dụng BRAM

- Hamsterworks wiki, bởi Mike Fields, nguồn gốc của mã OV7670

- Biểu dữ liệu hiển thị các thông số kỹ thuật cơ bản về thời gian

Đề xuất:

Trượt Máy Ảnh Theo Dõi Đối Tượng Với Trục Xoay. 3D được in & xây dựng trên bộ điều khiển động cơ DC RoboClaw & Arduino: 5 bước (có hình ảnh)

Trượt Máy Ảnh Theo Dõi Đối Tượng Với Trục Xoay. 3D được in & xây dựng trên bộ điều khiển động cơ DC RoboClaw & Arduino: Dự án này là một trong những dự án yêu thích của tôi vì tôi đã kết hợp sở thích làm video với DIY. Tôi đã luôn xem xét và muốn mô phỏng những cảnh quay điện ảnh đó trong những bộ phim trong đó máy ảnh di chuyển trên màn hình trong khi lia để theo dõi

ESP8266 RGB LED STRIP Điều khiển WIFI - NODEMCU làm điều khiển từ xa hồng ngoại cho dải đèn Led được điều khiển qua Wi-Fi - Điều khiển điện thoại thông minh RGB LED STRIP: 4 bước

ESP8266 RGB LED STRIP Điều khiển WIFI | NODEMCU làm điều khiển từ xa hồng ngoại cho dải đèn Led được điều khiển qua Wi-Fi | Điều khiển bằng điện thoại thông minh RGB LED STRIP: Xin chào các bạn trong hướng dẫn này, chúng ta sẽ học cách sử dụng gật đầu hoặc esp8266 làm điều khiển từ xa IR để điều khiển dải LED RGB và Nodemcu sẽ được điều khiển bằng điện thoại thông minh qua wifi. Vì vậy, về cơ bản bạn có thể điều khiển DÂY CHUYỀN LED RGB bằng điện thoại thông minh của mình

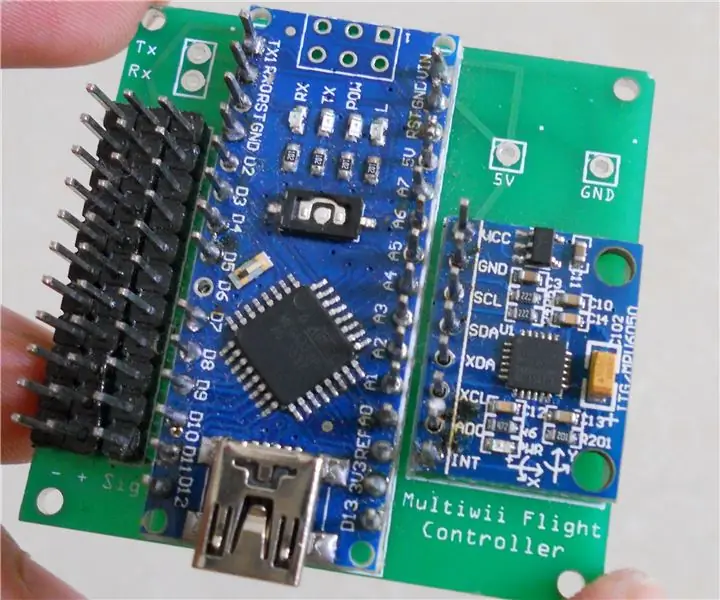

Tự làm bộ điều khiển bay điều khiển đa hệ điều khiển Arduino: 7 bước (có hình ảnh)

Tự làm bộ điều khiển máy bay đa năng điều khiển Arduino: Dự án này là tạo ra một bảng logic máy bay không người lái đa năng linh hoạt nhưng tùy chỉnh dựa trên Arduino và Multiwii

Điều khiển các thiết bị điện của bạn bằng Điều khiển từ xa Tv (Điều khiển từ xa) với Màn hình nhiệt độ và độ ẩm: 9 bước

Điều khiển thiết bị điện của bạn bằng Điều khiển từ xa Tv (Điều khiển từ xa) Có Hiển thị nhiệt độ và độ ẩm: xin chào, tôi là Abhay và đây là blog đầu tiên của tôi về Các thiết bị điện và hôm nay tôi sẽ hướng dẫn bạn cách điều khiển các thiết bị điện bằng điều khiển từ xa bằng cách xây dựng cái này dự án đơn giản. cảm ơn atl lab đã hỗ trợ và cung cấp tài liệu

Đầu xoay và nghiêng được điều khiển từ xa: 7 bước

Đầu xoay và nghiêng được điều khiển từ xa: Tôi luôn muốn có một chiếc xoay và đầu nghiêng được điều khiển từ xa. Có thể đó là dành cho máy quay phim của tôi, một người bắn súng bằng dây cao su hoặc một ống ngắm bằng súng nước. Bạn đặt gì trên boong trên cùng không thực sự quan trọng (miễn là nó không quá nặng), với dự án nhỏ này, yo