Mục lục:

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:30.

- Sửa đổi lần cuối 2025-01-23 15:14.

Trước đây, tôi đã viết một hướng dẫn về cách xây dựng một máy tính dựa trên Z80 và tôi đã thiết kế mạch điện đơn giản nhất có thể để có thể chế tạo nó một cách dễ dàng nhất có thể. Tôi cũng đã viết một chương trình nhỏ bằng cách sử dụng cùng một ý tưởng về sự đơn giản. Thiết kế này hoạt động khá tốt, nhưng tôi không hoàn toàn hài lòng với nó. Tôi bắt đầu với việc viết lại một chương trình cho phép nó được lập trình trong thời gian chạy. Điều này là để cho phép tôi kiểm tra các đoạn mã mà không cần phải cung cấp nó cho EEPROM, điều này sẽ yêu cầu tôi lập trình lại EEPROM. Điều này nghe có vẻ không phải là một ý tưởng thú vị đối với tôi. Sau đó, tôi bắt đầu nghĩ về không gian bộ nhớ. Nếu tôi muốn giao tiếp một phần cứng (chủ yếu là IO), một đoạn mã có thể vượt quá dung lượng bộ nhớ có sẵn cho hệ thống. Hãy nhớ rằng, thiết kế chỉ sử dụng byte thấp hơn của bus địa chỉ và sau đó bit thấp hơn của byte cao được sử dụng để chọn giữa không gian ROM và RAM. Điều này có nghĩa là tôi chỉ có 253 byte dung lượng để sử dụng. Bạn có thể hỏi tại sao lại là 253 thay vì 256. Đó là vì mã mới của tôi đưa ba byte dữ liệu vào cuối chương trình đã viết (điều này sẽ được đề cập sau, vì tôi đã sửa đổi nó để hoạt động trên thiết kế mới).

n

Tôi quay lại sơ đồ cũ của mình để xem những gì khác đang xảy ra. Tôi đã tìm thấy một lỗ hổng nhỏ với mạch chọn bộ nhớ mà tôi sẽ trình bày khi đến đó. Phiên bản đơn giản: tất cả các yêu cầu ghi sẽ thực sự được thực hiện, mặc dù nó luôn được đưa vào RAM. Điều này có lẽ không có gì đáng lo, nhưng tôi muốn làm đúng cách lần này. Và với điều đó, tôi bắt đầu vẽ một giản đồ mới. Hai bức ảnh đính kèm trang này là trước và sau của mạch thực tế. Tôi đã làm sạch rất nhiều hệ thống dây điện của mì Ý, điều đó thật không vui chút nào.

n

Nếu bạn làm theo cùng với bài nộp ban đầu của tôi và dự định làm theo cùng với cái này, bạn sẽ ghét tôi. Nếu bạn đang bắt đầu mới, thì bạn là người may mắn. Chỉ cần lấy các phần trong danh sách (hoặc phần tương đương của chúng) và làm theo.

Quân nhu:

LM7805 - Bộ điều chỉnh 5 VoltZ80 - CPU; bộ não của hệ thốngAT28C64B - EEPROM. Bộ nhớ dữ liệu "vĩnh viễn" được sử dụng cho chương trình cơ sở của máy tínhIDT6116SA - SRAM; được sử dụng để lưu trữ mã người dùng và / hoặc lưu trữ dữ liệu chungNE555 - Đồng hồ hệ thống74HC374 - Chốt bát phân với / OE; được sử dụng làm chip đầu vào74LS273 - Octal D-Latch với / MR; chip đầu raTLC59211 - chip điều khiển LED (được sử dụng để 74LS273 có thể điều khiển đèn LED, vì nó không có khả năng cho đầu ra hiện tại) MC14572 - Đây là chip “Trình điều khiển dòng”, nhưng tôi thấy nó hoàn hảo cho logic Điều khiển bộ nhớ. Nó có 4 biến tần, và một cổng NAND và NOR được xây dựng trong 74LS32 - Cổng Quad ORCD4001 - Cổng Quad NORCD4040 - Bộ đếm độ gợn sóng 12 giai đoạn; Bộ chia xung nhịp được vẽ, nhưng không được triển khai (để chạy hệ thống ở tốc độ xung nhịp chậm hơn) 2 Điện trở 10K Ohm - Một được sử dụng trong mạch hẹn giờ 555, vì vậy hãy sử dụng bất kỳ giá trị nào bạn muốn cho nó 4 Điện trở 1K Ohm - Một được sử dụng cho 555 mạch hẹn giờ, vì vậy hãy sử dụng bất cứ điều gì bạn muốn cho nó. Một cái khác được sử dụng để điều khiển đèn LED, vì vậy hãy thay đổi nó nếu bạn muốn 8x330 Ohm Bus điện trở 8x10K Ohm Bus 11 LED - Ba cái được sử dụng cho trạng thái hệ thống và tám cái còn lại là đầu ra. Đối với 8, tôi sử dụng màn hình biểu đồ thanh (HDSP-4836) 4 Tụ điện - Hai tụ điện được sử dụng là LM7805; 0,22uF và 0,1uF. Một là dành cho bộ đếm thời gian 555, vì vậy hãy sử dụng những gì bạn cảm thấy phù hợp. Cuối cùng là để thiết lập lại khi bật nguồn; 100uF2 N. O. Nút đẩy - Một được sử dụng cho đầu vào, nút còn lại để thiết lập lại 8 Công tắc SPST DIP - Đầu vào dữ liệu; Tôi đã sử dụng Piano Key styleWire. Rất nhiều và rất nhiều dây

n

LƯU Ý: phiên bản MC14572 xuyên lỗ đã lỗi thời, nhưng phiên bản SMD vẫn còn hoạt động (thậm chí không phải trạng thái “không dành cho thiết kế mới”), vì vậy bạn có thể cần phải mua một bảng mạch để cho phép bạn sử dụng nó. Một 74LS32 thứ hai có thể được sử dụng thay cho MC14572 (tham khảo sơ đồ “mạch chọn bộ nhớ” của ible trước)

Bước 1: Tổng quan nhanh về các thay đổi + sơ đồ

Cách đọc các giản đồ: Một mũi tên trỏ vào chip là đầu vào: Đầu vào> -Một mũi tên hướng ra khỏi chip là đầu ra: Đầu ra <-Busses sử dụng một dòng thay vì mũi tên: Bus | -

n

Hầu hết các chip đã được vẽ với sơ đồ chân chính xác của chúng. Sự sụt giảm nhỏ đã được rút ra trên những con chip này. Hầu hết các chip cũng có số pin và nhãn trên chúng. Chúng có thể hơi khó đọc. Bút chì của tôi đã trở nên xỉn màu.

n

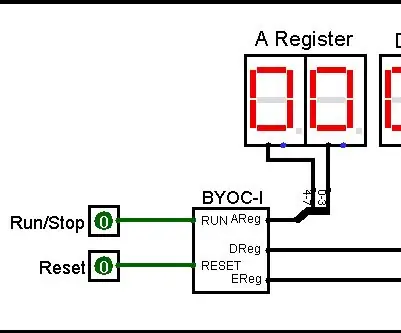

Về kết nối mạch điện, cách bố trí của thiết kế mới hầu như không thay đổi so với bản gốc. Tôi kết nối nibble dưới của byte cao địa chỉ với bộ nhớ và sau đó sử dụng bit thấp của nibble trên (A12) để lựa chọn RAM / ROM. Điều này có nghĩa là không gian ROM đã tăng từ 0000-00FF lên đến 0000-0FFF. Dung lượng Ram tăng từ 0100-01FF thành 1000-1FFF. Tôi cũng đã hoán đổi logic Kiểm soát bộ nhớ để có thiết kế tốt hơn và thêm hai đèn LED trạng thái mới (và một số logic keo). Tôi cũng đã vẽ (nhưng không đấu dây) mạch chia đồng hồ. Nó là để thực hiện hai chức năng. Chức năng rõ ràng là để chia tần số đồng hồ xuống. Chức năng khác dành cho mục đích PWM (Điều chế độ rộng xung), vì 555 không tạo ra sóng với chu kỳ nhiệm vụ 50%. Điều đó không thực sự quan trọng trong mạch này, nhưng nếu bạn muốn sử dụng đồng hồ để điều khiển một số đèn LED, bạn chắc chắn sẽ nhận thấy các hiệu ứng (một (bộ) (các) đèn LED sẽ mờ hơn đèn còn lại). Toàn bộ phần còn lại của mạch về cơ bản không thay đổi.

Bước 2: Kiểm soát CPU, Bộ nhớ và Bộ nhớ

Đây là phần mà độc giả của phiên bản trước ghét tôi. Trong bản dựng ban đầu, tôi chỉ ném các bộ phận lên bảng ở một nơi mà chúng trông có vẻ như sẽ không gặp vấn đề gì với việc kết nối dây. Kết quả trông giống như ai đó đổ một đĩa mì Ý lên đó và giống như "dây điện!" Tôi muốn dọn dẹp nó một chút, vì vậy tôi bắt đầu bằng cách sao chép mọi thứ ngoại trừ CPU, RAM và ROM. Tôi đã kéo lên gần như toàn bộ mạch đầu vào, mạch đầu ra và logic keo. Điều đó gần như khiến tôi bị tổn thương, nhưng điều đó là cần thiết. Tôi để nguyên tất cả các kết nối dữ liệu và byte thấp hơn của bus địa chỉ. Sau đó, tôi kết nối bốn bit tiếp theo của bus địa chỉ (A8-A11) với chip ROM. Tôi đã cẩn thận đi xung quanh con chip lần này để dễ dàng kéo lên để lập trình lại. Tôi cũng đã chuyển các kết nối địa chỉ xuống chip RAM.

n

Với điều đó, bây giờ tôi phải có dây logic điều khiển bộ nhớ. Trong sơ đồ ban đầu, tôi đã kết nối trực tiếp dòng / MREQ của bộ xử lý với / CE với cả hai chip bộ nhớ, sau đó tôi nối dây / WR với RAM’s / WE. Sau đó, tôi đã có CPU của / RD và / MREQ một cách hợp lý HOẶC cùng với A9. Về cơ bản, nó được thiết lập để tất cả các yêu cầu bộ nhớ kích hoạt cả RAM và ROM, nhưng A9 được sử dụng để chọn chip / OE nào được chọn. Điều này là tốt và tất cả bởi vì các chip sẽ vẫn không hoạt động cho đến khi một yêu cầu bộ nhớ được thực hiện và sau đó chỉ một / OE sẽ hoạt động trong một yêu cầu đọc. Điều này ngăn chặn nhiễu xuyên âm, nhưng mang lại một sắc thái khó xử. Vì A9 chỉ được sử dụng để xác định chip nào đang xuất dữ liệu và vì CPU có quyền truy cập trực tiếp vào chân RAM / WE nên bất kỳ và tất cả các yêu cầu ghi sẽ được thực hiện. Điều này là ổn đối với ROM vì chế độ ghi của nó bị hạn chế bằng cách buộc / WE trực tiếp vào nguồn cung cấp 5V. Tuy nhiên, RAM sẽ được ghi vào bất kể A9. Điều này có nghĩa là một cố gắng ghi vào một vị trí không gian ROM sẽ ghi vào cùng một vị trí trong không gian RAM.

n

Một giải pháp cho điều này là rewire logic điều khiển để CPU có quyền truy cập trực tiếp vào các chân chip / OE và / WE, sau đó sử dụng MREQ và A12 để chọn chip / CE được điều khiển. Tôi đã thực hiện ý tưởng này, nhưng thay vì sử dụng bốn cổng NOR và một biến tần như thiết kế ban đầu, tôi đã tìm thấy một con chip nhỏ khó xử lý hoàn hảo cho nhiệm vụ. Tôi phải tạo một mạch chỉ sử dụng các cổng logic có sẵn trong chip, nhưng điều đó đủ dễ dàng. A12 cấp trực tiếp vào cổng NAND và cổng NOR. / MREQ được đưa vào cổng NOR và lời khen của nó được đưa vào cổng NAND. Cổng NAND được sử dụng để điều khiển / CE cho RAM và đầu ra NOR được đảo ngược và được sử dụng để điều khiển ROM / CE. Điều này làm cho nó sao cho / MREQ phải ở mức thấp trước khi một trong hai chip được chọn và sau đó A12 chọn chip nào được chọn. Với thiết lập này, bây giờ mọi yêu cầu ghi vào ROM sẽ không làm gì cả. Nó cũng tiết kiệm điện năng vì chỉ có một chip hoạt động thay vì cả hai. Đối với bản thân chip logic, chúng ta vẫn có hai bộ biến tần chưa sử dụng bên trong. Một cái sẽ được sử dụng sau, nhưng chúng ta sẽ đến đó khi chúng ta đến đó.

Bước 3: Đèn LED trạng thái hệ thống

Trước khi bắt đầu dự án này, tôi đã cố gắng giao tiếp với một vi mạch nhất định, nhưng tôi đã gặp sự cố với nó. Không chắc chắn về những gì đang xảy ra, tôi đã sử dụng một đèn LED gắn bảng điều khiển để thăm dò xung quanh (một trong những cụm có một điện trở được tích hợp sẵn). Làm điều này cho tôi một ý tưởng hoài cổ vẫn được sử dụng cho đến ngày nay: đèn LED trạng thái được sử dụng để cho biết liệu bộ nhớ đang được đọc hay ghi vào. Nó được sử dụng cùng với đèn LED đầu vào mà tôi đã có. Đèn LED đầu vào được kết nối với bộ tạo tín hiệu / WAIT để cho chúng tôi biết rằng hệ thống đang chờ đầu vào (Tôi sẽ đến đó, đừng lo lắng). Tôi đã cân nhắc việc thêm một đèn LED để chỉ báo IO ghi, nhưng tôi nhận thấy rằng các đèn LED đầu ra thay đổi sẽ là một chỉ báo tuyệt vời về điều đó. Suy nghĩ về nó, tôi vẫn có thể thêm nó được nêu ra. Tuy nhiên, tôi thấy rất hữu ích khi biết liệu bộ nhớ đang được đọc hay ghi. Chà, dù sao thì nó cũng hữu ích cho việc gỡ lỗi chương trình. Tôi thực sự đã sử dụng nó nhiều như vậy khi cố gắng làm cho chương trình của tôi hoạt động: “tại sao nó lại ghi vào bộ nhớ? Nó không được cho là phải làm điều đó được nêu ra!”

n

Để điều khiển các đèn LED này, tôi đã sử dụng cổng NOR quad. Tôi đã sử dụng tất cả các cổng. Chỉ có hai cái được sử dụng để tạo ra các tín hiệu trạng thái, nhưng chip không có khả năng cấp nguồn để thực sự điều khiển các đèn LED. Chúng có khả năng làm chìm lượng điện nhiều như vậy, vì vậy tôi đã sử dụng hai cổng NOR khác làm bộ biến tần và kết nối các đèn LED như vậy. Vì một đèn LED được sử dụng để chỉ báo lần đọc và đèn còn lại để ghi và yêu cầu đọc và ghi sẽ không xảy ra cùng một lúc, nên tôi có thể sử dụng chỉ một điện trở cho cả hai đèn LED. Đối với các tín hiệu tôi cần để giải mã, điều đó cũng đủ dễ dàng. Tôi muốn tất cả các yêu cầu đọc bộ nhớ được chỉ định, vì vậy cổng NOR đầu tiên có / MREQ và / RD trên các đầu vào của nó. Trạng thái viết phức tạp hơn một chút, nhưng cũng dễ dàng. Tôi vẫn sử dụng / MREQ làm một đầu vào, nhưng việc sử dụng / WR làm đầu vào khác sẽ gây ra một sắc thái nhỏ mà tôi muốn tránh. Nó sẽ chỉ ra TẤT CẢ các yêu cầu viết. Tôi chỉ muốn những thứ đã thực sự trải qua. Vì vậy, làm thế nào tôi sẽ làm điều đó? À, hãy nhớ cách tôi đã thiết lập hệ thống để chỉ có thể ghi RAM? Tôi đã sử dụng RAM / CE làm đầu vào khác cho cổng NOR. Điều này có nghĩa là đèn LED sẽ chỉ sáng khi RAM được chọn và yêu cầu ghi đang được thực hiện. Về màu sắc của đèn LED, tôi đã chọn màu cam làm chỉ báo đọc (nhưng tôi chỉ tìm thấy những màu vàng) và màu đỏ làm chỉ báo ghi.

Bước 4: Đầu vào và đầu ra

Trong bước trước, bạn có thể nhận thấy rằng tôi đã thêm một số thành phần còn lại vào bo mạch. Tôi đang dành không gian để tôi sẽ không vô tình đặt dây vào nơi tôi muốn một thành phần (do đó, tôi sẽ phải tìm một vị trí mới cho thành phần đã nói). Bạn cũng có thể nhận thấy rằng tôi đã để nguyên các công tắc đầu vào và nối dây với đường ray điện. Tôi quyết định rằng vị trí ban đầu là vị trí hoàn hảo và quyết định đặt các đèn LED đầu ra gần đó (ở trên). Ở bên phải của màn hình thanh là chốt đầu vào. Trên đó là chốt đầu ra và bên trái của nó là trình điều khiển đèn LED. Tôi bắt đầu bằng cách kết nối màn hình với trình điều khiển vì đó là cách dễ thực hiện nhất. Sau đó, tôi kết nối các công tắc với phía đầu vào của chốt đầu vào. Tiếp theo, tôi kết nối phía đầu ra của chốt đầu ra với trình điều khiển đèn LED. Điều này có vẻ giống như một lệnh khó xử để có được những thứ có dây này, nhưng nó là có lý do. Đầu vào của chốt đầu ra phải được kết nối với bus dữ liệu cũng như đầu ra của chốt đầu vào. Ý tưởng là kết nối đầu ra của chốt đầu vào với đầu vào của chốt đầu ra, tôi đã làm. Sau đó, tất cả những gì tôi phải làm là kết nối mớ hỗn độn đó với bus dữ liệu. Không quan trọng việc các kết nối này đi đến đâu về mặt vật lý vì tất cả chúng đều sẽ được kết nối bằng điện. Máy tính bây giờ đã gần xong.

Bước 5: Đặt lại và hoàn thiện đầu vào và đầu ra

Xin lỗi, không có bức ảnh nào cho bước này. Tham khảo bước trước để biết các bức ảnh.

n

Bạn có thể nhận thấy trong ảnh cuối cùng của bước trước, tôi đã có một nút màu xanh lá cây và một chip logic khác được cài đặt. Con chip là cổng OR. Hai cổng được sử dụng để tạo ra tín hiệu / WAIT. Chà, người ta tạo ra tín hiệu bằng OR-ing / IORQ và / RD từ bộ xử lý. Đầu ra được đưa vào cổng thứ hai, nơi nó được HOẶC một lần nữa đến một nút nhấn. Nút này đưa đầu vào của cổng cao, do đó đưa đầu ra cao. Đầu ra này được cấp cho bộ xử lý / chân WAIT. Trong khi không được nhấn, một điện trở giữ đầu vào ở mức thấp. Ban đầu tôi sử dụng một điện trở 10K, nhưng LS32 thực sự đã đặt điện áp ra trên đầu vào. Điện trở không giảm xuống đủ thấp và tôi phải thay thế nó bằng 1K. Dù sao, ý tưởng là khi một yêu cầu đọc IO được thực hiện, cổng OR thứ nhất và thứ hai yêu cầu bộ xử lý đợi. Sau khi bạn đặt các công tắc đầu vào thành bất kỳ thứ gì bạn muốn, bạn nhấn nút và nó sẽ đưa CPU ra khỏi tình trạng chờ. Đèn LED “đầu vào” màu xanh lá cây, như tôi đã gọi ở bước trước, được nối dây để khi chân / WAIT ở mức thấp, nó sẽ sáng lên.

n

Nhưng chúng tôi vẫn chưa hoàn thành. Flip flop đầu vào cần một tín hiệu để cho nó biết khi nào dữ liệu đầu vào là hợp lệ và nên được đưa ra CPU. Chân đồng hồ này đang hoạt động ở mức cao. Trước đây, chúng tôi chỉ kết nối nó với nút. Đây vẫn là một tùy chọn hợp lệ, nhưng lần này tôi đã chọn đặt nó trên cùng một đầu ra như cổng OR thứ hai. IC này cũng có một chân / OE cần được điều khiển. Nếu nó được giữ ở mức cao, nó sẽ không bao giờ chèn dữ liệu vào xe buýt. Nếu được giữ ở mức thấp, nó sẽ luôn điều khiển xe buýt. Để khắc phục điều này, tôi chỉ cần sử dụng một cổng OR thứ ba. Các đầu vào là / IORQ và / RD và đầu ra chuyển trực tiếp đến chốt của / OE.

n

Chốt đầu ra cũng cần chân đồng hồ được điều khiển. Một lần nữa, nó đang hoạt động cao. Trong sơ đồ của tôi, tôi đã vẽ cổng OR thứ tư trực tiếp điều khiển chân bằng / IORQ và / WR. Điều này có nghĩa là chân đồng hồ sẽ được giữ ở mức cao cho đến khi yêu cầu ghi được thực hiện, sau đó nó sẽ xuống thấp rồi lại cao. Điều này có lẽ sẽ ổn vì bus dữ liệu vẫn có dữ liệu hợp lệ trên đó ngay sau khi cố gắng ghi, nhưng từ quan điểm kỹ thuật, đó là một thiết kế rác. Tôi không nhận thấy lỗi này cho đến khi tôi chụp những bức ảnh cuối cùng, nhưng tôi đã tách kết nối đó và sau đó đưa đầu ra cổng OR vào một trong các bộ biến tần không sử dụng từ logic điều khiển bộ nhớ, sau đó kết nối đầu ra của nó với chân đồng hồ. Tôi cũng đã sửa giản đồ và tìm thấy một lỗi khác mà tôi đã mắc phải. Tôi cũng đã sửa lại.

n

Với tất cả những điều đó cuối cùng đã hoàn thành, tôi có một lượng công việc rất nhỏ phải làm: mạch đặt lại. Tôi đã thêm một nút vào bảng và sử dụng một điện trở 10K để giữ một bên cao. Mặt còn lại trực tiếp tiếp đất. Mặt được giữ ở mức cao là đầu ra / RESET, đi đến mọi chip có chân / RESET (chốt CPU và đầu ra). Để hoàn thành việc đặt lại khi bật nguồn, tôi đã thêm tụ điện vào đầu ra / RESET. Ý tưởng là điện trở có giá trị lớn sẽ làm cho tụ điện tương đối lớn sạc chậm và giữ các chân / RESET ở mức thấp trong một số chu kỳ đồng hồ (CPU cần bốn chu kỳ đồng hồ). Bạn có thể đã đoán được mặt tiêu cực của mạch này là gì. Nó giống như phiên bản trước vì nó có cùng một mạch. Khi nhấn nút, tụ điện về cơ bản được nối tắt qua nút. Điều này không tốt cho cả nắp và nút, vì vậy nếu bạn muốn làm cho công trình của mình lâu dài hơn một chút, bạn có thể muốn thiết kế lại nó. Tôi đang nghĩ đến một bộ hẹn giờ 555 khác được thiết lập ở chế độ ổn định. Nhưng với điều đó, mạch máy tính bây giờ đã hoàn thành. Đúng vậy. Bây giờ nó cần được lập trình.

Bước 6: Lập trình

Lập trình thứ này là một cơn ác mộng. Tôi đã xây dựng một lập trình viên Arduino EEPROM. Nó không hoạt động. Tôi đã xây dựng một cái khác dựa trên thiết kế và mã hóa của người khác. Vẫn không hoạt động. Tôi đã quay lại phương pháp đã thử là đặt thủ công các địa chỉ và byte dữ liệu. Bằng cách nào đó, tôi đã làm nó rối tung lên. Tôi đã thử lại và vẫn sai. Tôi quay lại một lần nữa và phát hiện ra nó đã bị sai một byte, vì vậy tôi đã sửa nó và cuối cùng nó đã hoạt động, cảm ơn Chúa.

n

Đối với chương trình thực tế, có vẻ như nó siêu phức tạp và khó theo dõi, nhưng không phải vậy. Thực ra nó khá đơn giản. Một nửa trong số đó là sao chép các con số xung quanh. Một nửa còn lại được chia sẻ giữa toán học 16-bit, các bước nhảy có điều kiện và thậm chí nhiều hơn sao chép các số xung quanh. Vì vậy, hãy để tôi đi qua nó và cho bạn biết nó hoạt động như thế nào.

n

Việc khởi tạo chỉ đặt một số giá trị thanh ghi để chương trình sử dụng. Vòng lặp chương trình phức tạp hơn một chút, nhưng không phải là nhiều. Đầu tiên, nó chấp nhận đầu vào cho thanh ghi A trên cổng 00. Sau đó thanh ghi E được ghi vào bộ nhớ. Trên hai vòng đầu tiên, thanh ghi E chứa dữ liệu rác, vì vậy chúng tôi cố gắng ghi nó vào hai byte cuối cùng của không gian ROM vì nó sẽ không thực sự được ghi; con trỏ địa chỉ (IY) sau đó được tăng lên. Giá trị được lưu trữ trong D sau đó được chuyển sang E để được viết tiếp theo. Sau đó A được nạp vào D và L và E được sao chép vào H. HL là nơi so sánh giá trị diễn ra thông qua phép trừ và kiểm tra ZF (cờ không). Giá trị đầu tiên được so sánh với được lưu trữ trong thanh ghi B và C. B và C được coi như một thanh ghi 16 bit duy nhất, BC. Nếu các giá trị giống nhau, thì chương trình sẽ nhảy thẳng vào không gian RAM, nơi mã người dùng được cho là cư trú. Nếu mã trong BC không khớp, thì HL được tải lại với các giá trị ban đầu từ D và E và được so sánh một lần nữa với giá trị trong SP giống như cách nó được so sánh với BC. Nếu đó là một kết quả trùng khớp, nó có cùng kết quả, nhưng ba byte thừa được ghi vào bộ nhớ. Các byte là một đoạn mã khiến CPU quay trở lại chương trình ban đầu của nó (thiết lập lại phần mềm). Tuy nhiên, nếu lần so sánh thứ hai không khớp, chương trình sẽ lặp lại nơi nó lấy một giá trị từ người dùng.

n

LD SP, EDBFH; mã exe (thêm bước nhảy)

n

LD IY, FFEH; con trỏ bộ nhớ ban đầu để lưu trữ mã

n

LD BC, EDC3H; mã exe (không có vòng lặp)

n

vòng; chỉ thị hợp ngữ nên chúng ta không cần biết phần này nằm ở đâu trong bộ nhớ

n

TRONG A, (00H); lấy dữ liệu chương trình

n

LD (IY + 00H), E; E chứa mã cần lưu trữ

n

INC IY; chuyển đến vị trí bộ nhớ tiếp theo

n

LD E, D; ld D thành E

n

LD D, A; ld A thành D

n

LD H, E; ld E thành H

n

LD L, D; ld D thành L

n

HOẶC A; đặt lại cờ mang

n

SBC HL, BC; trả về 0 nếu mã exe 2 được nhập

n

JP Z, 1000H; nếu vậy, hãy chuyển đến và thực thi chương trình

n

LD H, E; nếu không, hãy làm mới chúng thành các giá trị thích hợp

n

LD L, D

n

HOẶC A; trừ đầu tiên có thể đã đặt cờ mang. Xóa nó

n

SBC HL, SP; trả về 0 nếu mã exe 1 đã được nhập

n

JP NZ, vòng lặp; nếu không, hãy lặp lại quy trình (bắt đầu với việc nhận một giá trị)

n

LD (IY + 00H), C3H; nếu không, hãy chèn một mã nhảy vào cuối chương trình người dùng

n

LD (IY + 01H), 00H; jump về cơ bản hoạt động như một thiết lập lại phần mềm

n

LD (IY + 02H), 00H; đó là một thiết lập lại đầy đủ trong trường hợp đăng ký bị sửa đổi

n

JP 1000H; nhảy đến và thực thi chương trình người dùng

Đề xuất:

BGA X-Ray Kiểm tra- Tìm hiểu Cách Kiểm tra ?: 7 Bước

Kiểm tra BGA X-Ray- Tìm hiểu Cách Kiểm tra ?: Tài liệu hướng dẫn này sẽ dạy bạn cách chuẩn bị sử dụng và hệ thống X-quang 2D để kiểm tra BGA, cũng như một số gợi ý về những gì cần tìm khi thực hiện kiểm tra BGA X-Ray cho bạn sẽ cần: Hệ thống tia X có khả năng giữ dây đeo tay PCBPCBESD áo khoác

Viết mã và kiểm tra máy tính bằng ngôn ngữ máy: 6 bước

Viết mã và kiểm tra máy tính bằng ngôn ngữ máy: Trong tài liệu hướng dẫn này, tôi sẽ chỉ cho bạn cách viết mã và kiểm tra một chương trình máy tính bằng ngôn ngữ máy. Ngôn ngữ máy là ngôn ngữ mẹ đẻ của máy tính. Bởi vì nó được cấu tạo bởi các chuỗi 1 và 0 nên con người không dễ dàng hiểu được. Để lo

Công cụ kiểm tra: Máy kiểm tra 555 Khá đơn giản. Đã sửa và cập nhật.: 3 bước

Công cụ kiểm tra: Máy kiểm tra 555 Khá đơn giản. Đã sửa và cập nhật: Ở đây tôi sẽ đưa ra một mạch nhỏ để kiểm tra xem bộ đếm thời gian 555 bạn vừa thử trong một mạch khác (và nó nóng lên hoặc không hoạt động gì cả) hoạt động hay không. Bạn đã bao giờ tự hỏi liệu đó có phải là mạch của bạn hay không, hay liệu có thể đã khiến bạn

Máy kiểm tra nguồn cung cấp máy tính đơn giản: 5 bước

Bộ kiểm tra nguồn điện máy tính đơn giản: Tài liệu hướng dẫn này là hướng dẫn nhanh để xây dựng bộ kiểm tra nguồn điện máy tính 20 pin từ các bộ phận của máy tính và PSU cũ. Người thử nghiệm cũng sẽ làm việc trên các nguồn điện có đầu nối 20 + 4 chân. Bạn có thể sử dụng phương pháp này để tạo một PSU 24 chân

Máy kiểm tra dung lượng pin Li-Ion (Máy kiểm tra nguồn điện Lithium): 5 bước

Máy kiểm tra dung lượng pin Li-Ion (Máy kiểm tra nguồn Lithium): =========== CẢNH BÁO & KHUYẾN CÁO ========== Pin Li-Ion rất nguy hiểm nếu không được xử lý đúng cách. =====================================