Mục lục:

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:31.

- Sửa đổi lần cuối 2025-01-23 15:14.

Bởi AmCoderhttps://www.linkedin.com/in/mituFollow More của tác giả:

Giới thiệu: Mitu Raj - Chỉ là một người có sở thích và ham học hỏi - Nhà thiết kế chip - Nhà phát triển phần mềm - Người đam mê Vật lý và Toán học Tìm hiểu thêm về AmCoder »

## Đây là liên kết được nhấp nhiều nhất, phổ biến nhất trên Google để triển khai VHDL THUẬT TOÁN CORDIC để tạo ra sóng sin và sóng cosine ## Hiện tại, nhiều thuật toán hiệu quả phần cứng tồn tại, nhưng những thuật toán này không được biết đến nhiều do sự thống trị của các hệ thống phần mềm. trong nhiều năm. CORDIC là một thuật toán không có gì khác ngoài một tập hợp các phép dịch chuyển và thêm lôgic được sử dụng để tính toán một loạt các hàm bao gồm một số hàm lượng giác, hypebol, tuyến tính và logarit. Đây là thuật toán được sử dụng trong máy tính, vv Vì vậy, chỉ bằng cách sử dụng bộ chuyển và bộ cộng đơn giản, chúng ta có thể thiết kế một phần cứng với độ phức tạp ít hơn nhưng sức mạnh của DSP bằng cách sử dụng thuật toán cordic. Do đó, nó có thể được thiết kế dưới dạng thiết kế RTL trần trong VHDL hoặc Verilog mà không cần sử dụng bất kỳ đơn vị dấu chấm động chuyên dụng hoặc IP toán học phức tạp nào.

Bước 1: VHDL và Modelsim

Ở đây, thuật toán cordic được thực hiện bằng cách sử dụng VHDL để tạo ra sóng sin và sóng cose. Nó có thể xuất ra sin và cosin của góc đầu vào với độ chính xác cao. Mã có thể được tổng hợp trên FPGA. Modelsim được sử dụng để mô phỏng thiết kế và băng ghế thử nghiệm.

Bước 2: Mã VHDL cho Thiết kế và Ghế thử nghiệm

Kỹ thuật chia tỷ lệ nhị phân được sử dụng để biểu diễn số dấu phẩy động.

Vui lòng xem qua các tài liệu đính kèm trước khi bạn viết mã.

Go thruSimulation cordic_v4.vhd - Thiết kế-Đầu vào là góc trong 32 bit + bit dấu; nó có thể xử lý bất kỳ góc nào từ 0 đến +/- 360 độ với độ chính xác đầu vào là 0,000000000233 độ. Khi đưa đầu vào -> MSB là bit dấu và 32 bit còn lại đại diện cho độ lớn.-Đầu ra của thiết kế là giá trị sin và cos của nó trong 16 bit + bit dấu.ie; với độ chính xác 0,00001526. Xin lưu ý rằng đầu ra được hiển thị ở dạng khen của 2 nếu giá trị sin hoặc cos tương ứng là âm. Mô phỏng testb.vhd - Test Bench For The Design (1) Góc đầu vào và kéo reset = '0'. Sau hai bước mô phỏng, kéo thiết lập lại thành '1' và "chạy tất cả". (2) Trong cửa sổ mô phỏng, đặt cơ số của tín hiệu sin và cos là số thập phân và định dạng> Tương tự (tự động). (3) Thu nhỏ để xem dạng sóng đúng.

Bước 3: Tệp được đính kèm

(1) cordic_v4.vhd - Thiết kế. (2) testb.vhd - Băng thử cho thiết kế.

(3) Tài liệu về cách buộc các đầu vào góc và chuyển đổi các kết quả nhị phân.

Cập nhật: CÁC BỘ PHIM NÀY LÀ BÊN NGOÀI VÀ KHÔNG ĐƯỢC CUNG CẤP THÊM. HÃY SỬ DỤNG CÁC BỘ LỌC TỪ BƯỚC TIẾP THEO

Bước 4: Lõi IP Mini-Cordic - 16 Bit

Giới hạn của việc triển khai ở trên là- chậm, tần số hoạt động đồng hồ thấp hơn do thực hiện các phép tính trong một chu kỳ đồng hồ duy nhất. Core-Cordic IP Core - 16 Bit

- Các đường dẫn quan trọng được phân phối cho nhiều chu kỳ để cải thiện hiệu suất. - Nhanh hơn - Thiết kế đã được chứng minh FPGA tổng hợp xung nhịp lên đến 100 Mhz. - Tối ưu hóa nhiều khu vực hơn trong HDL, phần cứng ít hơn. - Thêm tín hiệu Trạng thái tải và hoàn thành. - Chỉ có nhược điểm là độ phân giải thấp hơn so với trước đó.

hoàn toàn tự động từ đầu vào góc 0 đến 360 độ

Tệp Đính kèm: 1) Tệp vhdl chính mini cordic2) Băng thử nghiệm mini Cordic3) Hướng dẫn sử dụng lõi IP Mini Cordic4) Tài liệu về cách đặt góc và chuyển đổi kết quả

Đối với bất kỳ câu hỏi nào, vui lòng liên hệ với tôi:

Mitu Raj

theo dõi tôi:

mail: iammituraj@gmail.com

### Tổng số lượt tải xuống: 325 tính đến ngày 01-05-2021 ###

### Mã được chỉnh sửa lần cuối: July-07-2020 ###

Đề xuất:

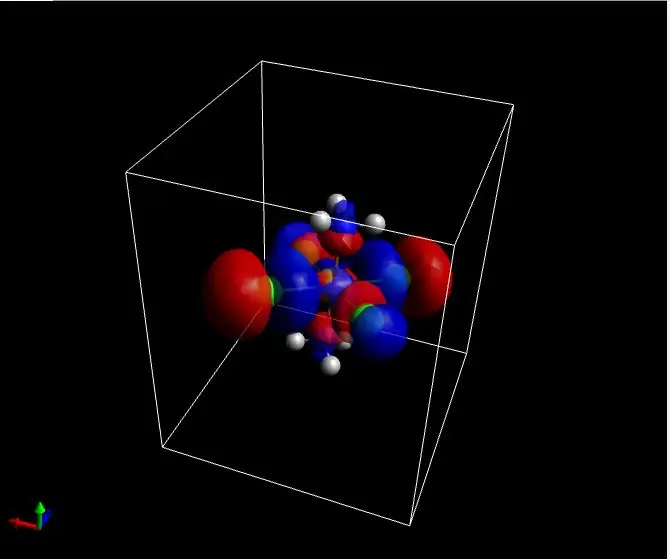

Tính toán Cơ học lượng tử tính toán: 4 bước

Tính toán Cơ học lượng tử tính toán: Các phép tính toán trong hóa học và vật lý có thể tiết lộ các tính chất rất thú vị trên một số mẫu vật (đặc biệt nếu chúng có thể được sửa đổi để có hiệu quả tốt hơn của một hợp chất ban đầu nhất định). trong các thủ tục, bên cạnh các yếu tố của d

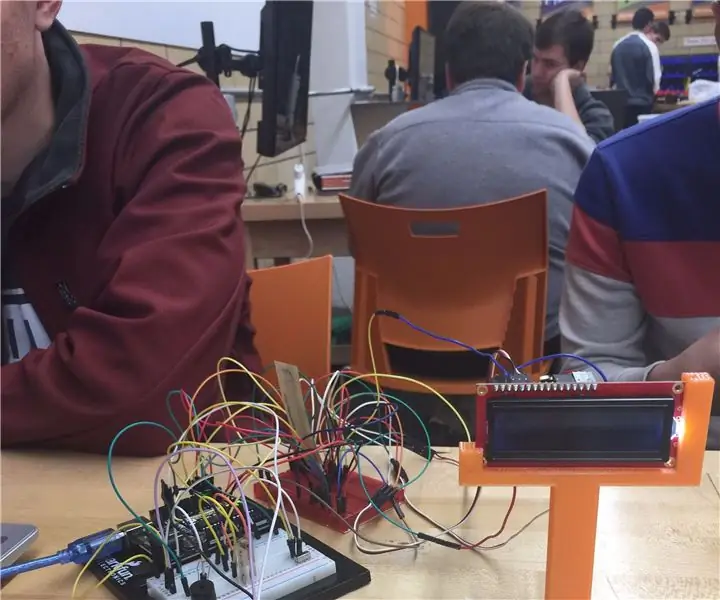

Nút an toàn không dây cho an toàn PLC: 6 bước (có hình ảnh)

Nút an toàn không dây cho an toàn PLC: Dự án này là bằng chứng của tôi về khái niệm sử dụng IoT và (cuối cùng) người máy để tạo ra một lớp an toàn bổ sung cho các cơ sở sản xuất nguy hiểm. Nút này có thể được sử dụng để bắt đầu hoặc dừng nhiều quá trình, bao gồm cả việc điều khiển tín hiệu

An toàn hơn Tốt hơn: Làm cho Ga Tàu An toàn hơn: 7 bước

An toàn hơn Tốt hơn: Làm cho Ga Tàu An toàn hơn: Nhiều ga xe lửa ngày nay không an toàn do thiếu an ninh, rào chắn và cảnh báo có tàu đến. Chúng tôi thấy cần phải khắc phục điều đó. Để giải quyết vấn đề này, chúng tôi đã tạo ra An toàn hơn tốt hơn. Chúng tôi đã sử dụng cảm biến rung, cảm biến chuyển động và

Khung hình nghệ thuật điểm ảnh LED với nghệ thuật arcade cổ điển, điều khiển ứng dụng: 7 bước (có hình ảnh)

Khung nghệ thuật điểm ảnh LED với nghệ thuật arcade cổ điển, điều khiển ứng dụng: TẠO KHUNG NGHỆ THUẬT LED ĐƯỢC ĐIỀU KHIỂN ỨNG DỤNG VỚI 1024 đèn LED hiển thị RETRO 80s ARCADE GAME ART PartsPIXEL Makers Kit - $ 59Adafruit 32x32 P4 LED Matrix - $ 49,9512x20 Inch Tấm acrylic, 1/8 " dày inch - Khói sáng trong suốt từ nhựa vòi -

Robot tự cân bằng sử dụng thuật toán PID (STM MC): 9 bước

Robot tự cân bằng sử dụng thuật toán PID (STM MC): Gần đây rất nhiều công việc đã được thực hiện trong việc tự cân bằng của các đối tượng. Khái niệm về sự tự cân bằng được bắt đầu với sự cân bằng của con lắc ngược. Khái niệm này cũng được mở rộng sang thiết kế máy bay. Trong dự án này, chúng tôi đã thiết kế một mod nhỏ