Mục lục:

- Bước 1: Vivado HLS là gì?

- Bước 2: Thư viện video HLS

- Bước 3: Tổng hợp

- Bước 4: Lập phiên bản và các thông tin khác để xuất

- Bước 5: Xuất sang Thư viện IP Vivado

- Bước 6: Tổng hợp và phân tích xuất

- Bước 7: Thêm Thư viện IP trong Vivado

- Bước 8: Thực hiện nâng cấp

- Bước 9: Chi tiết và thông tin bổ sung

- Bước 10: Đầu ra và đầu vào

- Bước 11: Đăng ký AXI Interfacing

- Bước 12: Dataflow Pragma

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:35.

- Sửa đổi lần cuối 2025-01-23 15:15.

Bạn đã bao giờ muốn xử lý thời gian thực trên video mà không cần thêm nhiều độ trễ hoặc trong một hệ thống nhúng? FPGA (Mảng cổng có thể lập trình trường) đôi khi được sử dụng để thực hiện việc này; tuy nhiên, việc viết các thuật toán xử lý video bằng các ngôn ngữ đặc tả phần cứng như VHDL hoặc Verilog là điều tốt nhất khiến bạn khó chịu. Nhập Vivado HLS, công cụ Xilinx cho phép bạn lập trình trong môi trường C ++ và tạo mã ngôn ngữ đặc tả phần cứng từ nó.

Phần mềm cần thiết:

- Vivado HLS

- Vivado

- (Nếu bạn sử dụng đăng ký AXI) Vivado SDK

(Tùy chọn) Tải xuống các ví dụ được tạo bởi Xilinx tại đây:

Ví dụ về video Xilinx HLS

Bước 1: Vivado HLS là gì?

Vivado HLS là một công cụ được sử dụng để biến mã giống như c ++ thành cấu trúc phần cứng có thể được triển khai trên FPGA. Nó bao gồm một IDE để thực hiện việc phát triển này. để sử dụng với Vivado.

Tải xuống các tệp đính kèm và đặt chúng gần nơi bạn sẽ tạo dự án của mình. (đổi tên chúng trở lại "top.cpp" và "top.h" nếu chúng có tên ngẫu nhiên)

Bước 2: Thư viện video HLS

Thư viện Video của HLS có tài liệu với các thiết kế tham chiếu trong bài báo này: XAPP1167 Một tài nguyên hữu ích khác là trang Xilinx Wiki về nó.

Khởi động Vivado HLS.

Tạo một dự án mới.

Lấy các tệp bạn đã tải xuống ở bước trước và thêm chúng dưới dạng tệp nguồn. (Lưu ý: các tệp không được sao chép vào dự án, nhưng thay vào đó vẫn giữ nguyên vị trí của chúng)

Sau đó, sử dụng nút Browse để chọn chức năng hàng đầu.

Trên trang tiếp theo, chọn phần Xilinx bạn đang sử dụng.

Bước 3: Tổng hợp

Giải pháp => Chạy Tổng hợp C => Giải pháp hoạt động

Sau ~ 227,18 giây, nó sẽ được thực hiện. (Lưu ý: thời gian tổng hợp thực tế của bạn sẽ thay đổi tùy theo nhiều yếu tố)

Bước 4: Lập phiên bản và các thông tin khác để xuất

Số phiên bản tương tác với Vivado để khiến bạn có thể cập nhật IP trong một thiết kế. Nếu đó là một thay đổi phiên bản nhỏ, nó có thể được thực hiện tại chỗ trong khi các thay đổi phiên bản lớn yêu cầu bạn thêm thủ công vào khối mới và xóa khối cũ. được thực hiện hoàn toàn tự động bằng cách nhấn nút cập nhật IP. Bạn có thể chạy "report_ip_status" trong bảng điều khiển Vivado tcl để xem trạng thái IP của mình.

Đặt số phiên bản và thông tin khác trong Giải pháp => Cài đặt Giải pháp…

Ngoài ra, các cài đặt này có thể được đặt trong quá trình xuất.

Bước 5: Xuất sang Thư viện IP Vivado

Giải pháp => Xuất RTL

Nếu bạn không đặt chi tiết thư viện IP trong bước trước, bạn có thể thực hiện điều đó ngay bây giờ.

Bước 6: Tổng hợp và phân tích xuất

Trên màn hình này, chúng ta có thể thấy số liệu thống kê về mô-đun đã xuất của chúng tôi, cho thấy rằng nó đáp ứng khoảng thời gian đồng hồ của chúng tôi là 10ns (100MHz) và lượng tài nguyên mà nó sử dụng.

Với sự kết hợp của điều này, Báo cáo tổng hợp và phân tích Luồng dữ liệu của chúng tôi, chúng ta có thể thấy rằng phải mất 317338 chu kỳ đồng hồ * khoảng thời gian đồng hồ 10ns * 14 giai đoạn đường ống = 0,04442732 giây. Có nghĩa là tổng độ trễ được thêm vào bởi quá trình xử lý hình ảnh của chúng tôi nhỏ hơn một phần hai mươi giây (khi đạt tốc độ 100MHz được nhắm mục tiêu).

Bước 7: Thêm Thư viện IP trong Vivado

Để sử dụng khối IP tổng hợp của bạn, bạn cần phải thêm nó vào Vivado.

Trong Vivado, hãy thêm kho lưu trữ IP vào dự án của bạn bằng cách đi tới danh mục IP và nhấp chuột phải chọn "Thêm kho lưu trữ…"

Điều hướng đến thư mục dự án Vivado HLS của bạn và chọn thư mục giải pháp của bạn.

Nó sẽ báo cáo IP mà nó tìm thấy.

Bước 8: Thực hiện nâng cấp

Đôi khi bạn cần thực hiện các thay đổi đối với khối HLS của mình sau khi đưa nó vào thiết kế Vivado.

Để thực hiện việc này, bạn có thể thực hiện các thay đổi và tổng hợp lại và xuất IP với số phiên bản cao hơn (xem chi tiết trong bước trước về các thay đổi số phiên bản lớn / nhỏ).

Sau khi thay đổi xuất phiên bản mới, hãy làm mới kho IP của bạn trong Vivado. Điều này có thể được thực hiện khi Vivado nhận thấy IP đã thay đổi trong kho lưu trữ hoặc được kích hoạt theo cách thủ công. (Lưu ý, nếu bạn làm mới kho lưu trữ IP của mình sau khi bắt đầu, nhưng trước khi quá trình xuất hoàn tất trong HLS, IP sẽ tạm thời không ở đó, hãy đợi nó kết thúc và làm mới lại.)

Tại thời điểm này, một cửa sổ sẽ xuất hiện với thông tin rằng một IP đã được thay đổi trên đĩa và cung cấp cho bạn tùy chọn cập nhật nó bằng nút "Đã chọn nâng cấp". Nếu thay đổi là một thay đổi phiên bản nhỏ và không có giao diện nào thay đổi, sau đó nhấn nút đó sẽ tự động thay thế IP cũ bằng IP mới, nếu không có thể phải thực hiện thêm công việc.

Bước 9: Chi tiết và thông tin bổ sung

Các bước sau cung cấp thêm thông tin về cách hoạt động của tổng hợp HLS và bạn có thể làm gì với nó.

Để biết ví dụ về một dự án sử dụng khối IP tổng hợp HLS, hãy xem hướng dẫn này.

Bước 10: Đầu ra và đầu vào

Đầu ra và Đầu vào cho khối IP cuối cùng được xác định từ một phân tích mà bộ tổng hợp thực hiện về luồng dữ liệu vào và ra khỏi chức năng hàng đầu.

Tương tự như trong VHDL hoặc Verilog, HLS cho phép bạn chỉ định chi tiết về các kết nối giữa các IP. Những dòng này là ví dụ về điều này:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma Cổng GIAO DIỆN HLS của trục = video_in bó = INPUT_STREAM #pragma Cổng trục GIAO DIỆN HLS = video_out bó = OUTPUT_STREAM #pragma GIAO DIỆN HLS s_axilite port = x Bundle = CONTROL_BUS offset = 0x14 # pragma HLS INTERFACE y_ pack = CONTROLx1

Bạn có thể thấy các cổng được hiển thị trên khối IP bị ảnh hưởng như thế nào bởi các chỉ thị này.

Bước 11: Đăng ký AXI Interfacing

Để có được đầu vào / đầu ra đến / từ khối IP của bạn đến PS, một cách tốt để thực hiện điều này là thông qua giao diện AXI.

Bạn có thể chỉ định điều này trong mã HLS của mình, bao gồm các hiệu số sẽ được sử dụng để truy cập giá trị sau này như sau:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma GIAO DIỆN HLS cổng s_axilite = x bó = CONTROL_BUS offset = 0x14

#pragma GIAO DIỆN HLS s_axilite port = y Bundle = CONTROL_BUS offset = 0x1C #pragma HLS dataflow

x = 42;

y = 0xDEADBEEF; }

Sau khi được kết nối đúng cách trong Vivado, bạn có thể truy cập các giá trị bằng mã này trong Vivado SDK:

#include "thông số.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR + xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR + yregoff);

Điều này sẽ khiến bạn kết thúc bằng 42 trong x và 0xdeadbeef trong y

Bước 12: Dataflow Pragma

Bên trong #pragma DATAFLOW cách mã được triển khai thay đổi so với C ++ bình thường. Mã được kết nối để tất cả các lệnh luôn chạy ở các phần khác nhau của dữ liệu (Hãy nghĩ về nó giống như một dây chuyền lắp ráp trong một nhà máy, mỗi trạm làm việc liên tục để thực hiện một chức năng và chuyển nó đến trạm tiếp theo)

từ hình ảnh, bạn có thể thấy rằng mỗi lệnh

Mặc dù có vẻ là các biến bình thường, các đối tượng img thực sự được thực hiện dưới dạng bộ đệm nhỏ giữa các lệnh. Việc sử dụng một hình ảnh làm đầu vào cho một hàm sẽ "tiêu thụ" nó và khiến nó không thể sử dụng được nữa. (Do đó cần có các lệnh trùng lặp)

Đề xuất:

Tự làm cáp video tổng hợp TI-99 / 4a: 7 bước

Cáp video tổng hợp DIY TI-99 / 4a: Là loại người rất thích công nghệ retro (hãy xem trang web của tôi: www.retrodepot.net), tôi cảm thấy khó có thể bỏ qua một thỏa thuận tốt về thiết bị điện tử cổ điển. Gần đây, tôi đã sở hữu chiếc compu TI-99 / 4a thứ hai của Texas Instruments

Hình khối và Hình dạng các tông 1: 4 Bước (có Hình ảnh)

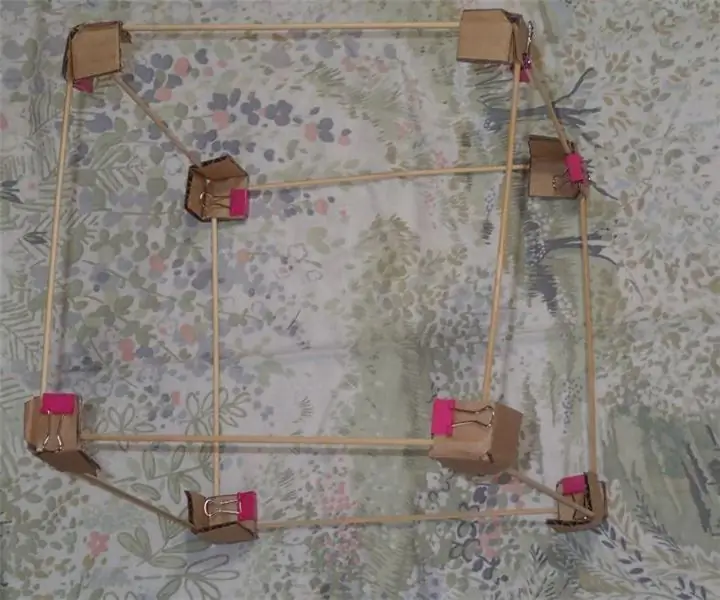

Các hình khối và hình dạng các tông 1: Trong khi thử nghiệm với một số xiên gỗ và bìa cứng, tôi đã tìm thấy một vài cách để tạo hình khối và các hình dạng khác từ những vật liệu đơn giản. Bằng cách đưa những thứ này ra dưới dạng Có thể hướng dẫn, tôi hy vọng sẽ thúc đẩy việc chơi và học mang tính xây dựng. Các biến thể trong hướng dẫn này

Khối lập phương ánh sáng LED bê tông: 12 bước (có hình ảnh)

Khối đèn LED bê tông: Khối đèn LED bê tông này rất đơn giản, nhưng khá nổi bật và tôi nghĩ nó sẽ trở thành điểm nhấn hoặc đèn ngủ hoàn hảo. Bê tông rất thú vị khi sử dụng, và tất nhiên bạn có thể thay đổi thiết kế tùy theo sở thích của mình và thêm màu sắc, thay đổi t

Hộp Barbie: Hộp ngụy trang / Hộp bùng nổ cho máy nghe nhạc Mp3 của bạn: 4 bước (có hình ảnh)

Hộp Barbie: Hộp ngụy trang / Hộp bùng nổ cho máy nghe nhạc Mp3 của bạn: Đây là một hộp đựng bảo vệ có đệm cho máy nghe nhạc mp3 của bạn, cũng có thể chuyển đổi giắc cắm tai nghe sang 1/4 inch, có thể hoạt động như một hộp bùng nổ khi lật công tắc và ngụy trang máy nghe nhạc mp3 của bạn thành một máy nghe nhạc đầu những năm chín mươi hoặc hành vi trộm cắp tương tự tôi

Cách chạy dữ liệu mạng và video tổng hợp qua cáp Ethernet: 6 bước (có hình ảnh)

Cách chạy dữ liệu mạng và video tổng hợp qua cáp Ethernet: Tôi cần chạy Video và âm thanh đến một phần khác trong nhà của mình. Vấn đề là, tôi không có nhiều cáp AV, cũng như thời gian và tiền bạc để thực hiện một cài đặt tốt. Tuy nhiên, tôi đã có rất nhiều Cáp Ethernet Cat 5 nằm xung quanh. Đây là những gì tôi đã nghĩ ra