Mục lục:

- Bước 1: Định cấu hình Logic có thể lập trình Zynq cho Máy phát

- Bước 2: Định cấu hình Logic có thể lập trình Zynq cho Bộ thu

- Bước 3: Thiết lập trình điều khiển VDMA

- Bước 4: Thiết lập mạng Nanorouter

- Bước 5: Thiết lập hệ thống xử lý Zynq để truyền dữ liệu qua Ethernet

- Bước 6: Thiết lập hệ thống xử lý Zynq để tiếp nhận dữ liệu qua Ethernet

- Bước 7: Kết nối các bo mạch Zybo của bạn với Nguồn HDMI và Ổ cắm HDMI

- Bước 8: Ý tưởng thay thế để cải tiến

- Bước 9: Khả năng tiếp cận

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:34.

- Sửa đổi lần cuối 2025-01-23 15:15.

Bạn đã bao giờ ước rằng mình có thể kết nối TV với PC hoặc máy tính xách tay như một màn hình bên ngoài, nhưng lại không muốn có tất cả những sợi dây khó chịu đó? Nếu vậy, hướng dẫn này chỉ dành cho bạn! Mặc dù có một số sản phẩm đạt được mục tiêu này, nhưng một dự án DIY sẽ thỏa mãn hơn nhiều và có khả năng rẻ hơn.

Khái niệm này khác với các sản phẩm như chromecast, vì nó nhằm thay thế cho dây HDMI kết nối với màn hình thay vì trở thành thiết bị phát trực tuyến.

Dự án của chúng tôi được tạo ra như một dự án cuối cùng cho khóa học Hệ điều hành thời gian thực tại Đại học Bách khoa Bang California, San Luis Obispo.

Mục tiêu của dự án là sử dụng hai bo mạch Digilent Zybo để hoạt động như giao diện truyền thông không dây giữa thiết bị phát HDMI (PC, blu-ray, v.v.) với thiết bị nhận HDMI (Màn hình máy tính để bàn, Máy chiếu, TV, v.v.).

Một Digilent Zybo sẽ được kết nối qua HDMI với thiết bị truyền và chiếc còn lại sẽ được kết nối qua HDMI với thiết bị nhận.

Giao tiếp không dây sẽ được thực hiện bằng cách sử dụng mạng cục bộ không dây dành riêng cho bộ phát và bộ thu, mà không được định tuyến thông qua bộ định tuyến gia đình hoặc thiết bị khác. Mô-đun không dây được sử dụng cho dự án này là máy tính nano tplink wr802n, một trong số đó hoạt động như một điểm truy cập để thiết lập mạng và mô-đun kia hoạt động như một máy khách để kết nối với mạng. Mỗi máy tính nano sẽ được kết nối qua cáp ethernet với bo mạch Zybo. Khi được kết nối với các bộ định tuyến này, các thiết bị sẽ giao tiếp qua TCP như thể chúng được kết nối với một cáp ethernet (có nghĩa là cấu hình duy nhất cần thiết để thiết lập kết nối là địa chỉ IP của máy khách).

Mặc dù mục tiêu của dự án là tạo điều kiện cho luồng video 1080x720 @ 60Hz, nhưng điều này không thể đạt được do giới hạn băng thông trong mạng không dây và thiếu tính năng nén video thời gian thực để giảm dữ liệu cần gửi. Thay vào đó, dự án này đóng vai trò là khuôn khổ cho sự phát triển trong tương lai để đạt được mục tiêu này, vì nó đã hạn chế nghiêm ngặt các giới hạn về tốc độ khung hình để truyền trực tiếp dữ liệu HDMI một cách chính xác như dự định.

Yêu cầu dự án:

2x Bảng phát triển Digilent Zybo (phải có ít nhất một cổng HDMI)

2x cáp HDMI

2x cáp microusb (để kết nối Zybo với PC để phát triển)

2x bộ định tuyến nano tplink wr802n (bao gồm bộ điều hợp nguồn adtl. 2x microusb và ổ cắm điện trên tường)

2x cáp ethernet

*** Lưu ý: Hướng dẫn này giả định bạn đã quen với bộ thiết kế Vivado và có kinh nghiệm tạo một dự án và thiết kế khối mới. ***

Bước 1: Định cấu hình Logic có thể lập trình Zynq cho Máy phát

Cách tiếp cận của chúng tôi để phát triển logic có thể lập trình của bộ truyền là thực hiện truyền hdmi sang hdmi từ PC để giám sát bằng cách sử dụng hai khối Truy cập Bộ nhớ Trực tiếp Video (VDMA), một để ghi và một để đọc.

Cả hai đều được chọn để chạy tự do, chế độ 3 khung hình bộ đệm (0-1-2). Vì lõi video được tối ưu hóa cho 60 khung hình mỗi giây, điều này có nghĩa là VDMA sẽ ghi hoặc đọc một khung hình mới sau mỗi 16,67 mili giây theo thứ tự sau: 0, 1, 2, 0, 1, 2, 0, 1, 2. Vị trí bộ nhớ DDR cho mỗi khung khác nhau đối với hai VDMA vì chúng không còn được đồng bộ hóa với nhau. Thay vào đó, một bộ đếm thời gian phần cứng (TTC1), được cấu hình cho 60 Hz, được sử dụng để đồng bộ hóa chuyển động của dữ liệu giữa hai vị trí bộ nhớ.

Hình trên cho thấy 3 khung, kích thước của chúng và dung lượng bộ nhớ mà mỗi khung yêu cầu (ở bên phải của khung). Nếu chúng ta gán VDMA ghi cho các vị trí bộ nhớ này, thì chúng ta có thể gán các vị trí bộ nhớ VDMA đọc ngoài tập hợp này, chẳng hạn bắt đầu bằng 0x0B000000. Mỗi khung hình được tạo thành từ 1280 * 720 pixel và mỗi pixel được tạo thành từ 8 bit Đỏ, Xanh lá cây và Xanh lam với tổng số 24 bit. Điều này có nghĩa là một khung được tạo thành từ 1280 * 720 * 3 byte (2,76 MB).

Bên trong bộ hẹn giờ IRQ, được mô tả trong thiết lập trình điều khiển VDMA, sẽ xử lý việc sao chép dữ liệu giữa hai vị trí bộ nhớ VMDA. VDMA cung cấp một con trỏ đến khung hiện tại đang được ghi vào hoặc đọc từ đó. Khung được thể hiện bằng một mã màu xám cụ thể, được chuyển đổi trong phần mềm. Định nghĩa mã màu xám cho cấu hình bộ đệm khung 3 có thể được tìm thấy trong Hướng dẫn Sản phẩm AXI VDMA ở phụ lục C.

Điều này cho phép chúng tôi sao chép nội dung đang được ghi vào bộ nhớ mà không cần đọc từ khung hiện đang được ghi vào.

*** Lưu ý rằng VDMA đã đọc không được sử dụng khi gửi dữ liệu qua mạng không dây. Mục đích duy nhất là để xác minh hoạt động thích hợp của việc sao chép bộ nhớ từ VMDA ghi. VMDA đã đọc nên bị vô hiệu hóa. ***

Dưới đây là các bước để tạo Khối thiết kế máy phát:

- Khi tạo một dự án mới, bạn nên gán một chip hoặc bo mạch cho dự án. Liên kết này mô tả cách thêm tệp bảng mới vào thư mục Vivado và liên kết đúng bảng với dự án của bạn. Nó sẽ hữu ích khi thêm khối Hệ thống xử lý và chuyển đổi từ phần cứng sang phần mềm (phía SDK).

-

Thêm các khối sau:

- dvi2rgb

- Video vào Axi4-stream

- Bộ điều khiển thời gian

- axi4-stream to vid out

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Thuật sĩ đồng hồ

- Hằng số

- Hệ thống xử lý Zynq

- Khi thêm Hệ thống xử lý, hãy nhấp vào "Chạy tự động hóa khối" từ thanh màu xanh lá cây trên cùng và đảm bảo rằng tùy chọn "Áp dụng cài đặt sẵn bảng" được chọn. Để mọi thứ khác mặc định.

- Hình ảnh của mỗi cửa sổ cấu hình khối có thể được tìm thấy trong các hình ảnh trên. Nếu bạn không thấy hình ảnh cho một cửa sổ cụ thể, hãy để nó làm mặc định.

-

Bắt đầu định cấu hình hệ thống xử lý Zynq:

- Trong Cấu hình PS-PL AXI Không an toàn Bật GP Master AXI, bật Giao diện M AXI GP0

- Trong Cấu hình PS-PL Giao diện HP Slave AXI, bật cả HP0 và HP1

- Trong cấu hình MIO Đảm bảo ENET0 được bật trong Thiết bị ngoại vi I / O, sau đó bật Bộ xử lý ứng dụng, bật Bộ hẹn giờ0

- Trong Đồng hồ vải PL cấu hình đồng hồ, bật FCLK_CLK0 và đặt thành 100 MHz.

- Bấm Ok

- Trước khi nhấp vào "Chạy tự động hóa kết nối", hãy đảm bảo kết nối các khối video như đã thấy trong hình ảnh thiết kế khối TX ở trên. Bạn sẽ muốn đổi tên hằng số thành VDD và đặt giá trị thành 1. Kết nối các khối video cho phù hợp.

- Đặt đồng hồ HDMI TMDS và chân dữ liệu bên ngoài trên các khối rgb2dvi và dvi2rgb

- Tạo một cổng đầu vào và đầu ra cho tín hiệu phát hiện phích cắm nóng (HPD) và kết nối chúng với nhau, chúng được xác định trong tệp ràng buộc

-

Đồng hồ pixel được khôi phục từ TMDS_Clk_p, được tạo trong tệp ràng buộc. Đây sẽ là 74,25 MHz phù hợp với độ phân giải 720p. Điều quan trọng là phải kết nối đồng hồ pixel (từ khối dvi2rgb) với các chân sau:

- vid_io_in_clk (vid vào khối luồng axi)

- vid_io_out_clk (luồng axi đến khối vid out)

- clk (Bộ điều khiển thời gian)

- PixelClk (rgb2dvi)

- *** Lưu ý: Hiện tại, để kích hoạt khôi phục đồng hồ pixel, các đầu nối HDMI rx và tx phải được cắm vào nguồn / ổ cắm đang hoạt động. Một cách giải quyết vấn đề này là tách các khối video rx và tx thành các miền đồng hồ khác nhau (nói cách khác, tạo một đồng hồ 74,25 MHz mới để cấp cho khối tx). ***

- Tiếp theo, thiết lập trình hướng dẫn đồng hồ để bạn có đầu vào 100 MHz (nguồn bộ đệm chung) và 3 đồng hồ đầu ra @ 50 MHz (đồng hồ AXI-Lite), 150 MHz (đồng hồ AXI4-Luồng), 200 MHz (chân dvi2rgb RefClk).

- Kết nối chân hệ thống xử lý FCLK_CLK0 với đầu vào trình hướng dẫn đồng hồ

- Tại thời điểm này, hãy nhấp vào "Chạy tự động hóa kết nối" từ thanh màu xanh lục ở đầu cửa sổ thiết kế. Bạn nên làm điều này cho từng khối một và làm theo hình ảnh thiết kế khối TX ở trên.

- Công cụ sẽ cố gắng thêm AXI Interconnect, hoạt động như một kết nối master / slave cho các khối sử dụng bus AXI-Lite (VDMA và GPIO).

- Nó cũng sẽ thêm AXI SmartConnect, hoạt động như một kết nối chính / phụ cho các giao diện bộ xử lý AXI4-Luồng và Hiệu suất cao được sử dụng bởi VDMA (Bản đồ truyền tới bộ nhớ và ngược lại).

- Công cụ này cũng sẽ thêm Thiết lập lại hệ thống bộ xử lý. Đảm bảo rằng điều này chỉ được kết nối với VDMA, GPIO và các khối liên quan đến bộ xử lý. Không kết nối nó với bất kỳ khối video nào (tức là dvi2rgb, bộ điều khiển thời gian, vid to stream, v.v.)

- Khi quá trình tự động hóa kết nối đã hoàn tất, hãy xác minh rằng các kết nối khớp với hình ảnh thiết kế khối TX. Bạn sẽ nhận thấy một khối ILA Hệ thống bổ sung chưa được đề cập đến. Điều này chỉ để gỡ lỗi và không cần thiết cho bây giờ. Nó sử dụng Thiết lập lại bộ xử lý 150M, vì vậy điều đó cũng không cần thiết. Bất cứ nơi nào bạn nhìn thấy "lỗi" nhỏ màu xanh lá cây trên các bus, đó là do ILA và có thể bị bỏ qua.

- Bước cuối cùng là nhấp chuột phải vào thiết kế khối trong cây nguồn dự án và chọn "Tạo HDL Wrapper." Nếu bạn định thêm logic vào trình bao bọc, nó sẽ bị ghi đè mỗi khi nó được chọn.

- Xem phần Thiết lập trình điều khiển VDMA để biết chi tiết về phía SDK.

Đồng hồ và Đặt lại

Tôi nhận thấy rằng các khía cạnh quan trọng nhất của bất kỳ dự án logic có thể lập trình nào là xem xét cẩn thận các miền đồng hồ và tín hiệu đặt lại. Nếu chúng được định cấu hình đúng, bạn sẽ có một cơ hội tốt để thiết kế của mình hoạt động.

Đồng hồ pixel và thời gian đã khóa

Để xác minh rằng một số tín hiệu nhất định đang hoạt động, bạn nên kết nối các tín hiệu này với đèn LED (đồng hồ, đặt lại, khóa, v.v.). Hai tín hiệu mà tôi thấy hữu ích để theo dõi trên bảng máy phát là đồng hồ pixel và tín hiệu "bị khóa" trên khối AXI4-Stream to video out, cho bạn biết rằng thời gian video đã được đồng bộ hóa với bộ điều khiển thời gian và nguồn video dữ liệu. Tôi đã thêm một số logic vào trình bao bọc khối thiết kế theo dõi đồng hồ pixel bằng cách sử dụng tín hiệu PixelClkLocked trên khối dvi2rgb dưới dạng đặt lại. Tôi đã đính kèm tệp dưới dạng hdmi_wrapper.v ở đây. Tệp ràng buộc cũng được đính kèm ở đây.

Bước 2: Định cấu hình Logic có thể lập trình Zynq cho Bộ thu

Khối Logic có thể lập trình cho máy thu đơn giản hơn. Sự khác biệt chính, ngoài các khối đầu vào hdmi bị thiếu là không có đồng hồ pixel được phục hồi. Vì lý do đó, chúng tôi phải tạo của riêng chúng tôi từ trình hướng dẫn đồng hồ. Thiết kế này nên được thực hiện trong một dự án riêng biệt với máy phát. Đối với mục đích của chúng tôi, dự án máy thu theo bảng Zybo 7Z-20 trong khi Máy phát theo bảng Z7-10. Các FPGA trên bảng là khác nhau nên … hãy cẩn thận.

Dưới đây là các bước để tạo Khối thiết kế bộ thu:

-

Thêm các khối ip sau vào thiết kế của bạn:

- Bộ điều khiển thời gian

- AXI4-Stream to Video Out

- RGB sang DVI

- AXI VDMA

- AXI GPIO

- Hệ thống xử lý

- Thuật sĩ đồng hồ

- Hằng số (VDD được đặt thành 1)

- Thực hiện theo cùng một mẫu để định cấu hình các khối này làm Máy phát. Hình ảnh cho sự khác biệt đáng chú ý về cấu hình đã được bao gồm ở đây. Những cái khác vẫn giống như Máy phát.

- Định cấu hình VDMA cho thiết kế này dưới dạng kênh chỉ đọc. Tắt kênh ghi.

-

Trình hướng dẫn đồng hồ phải được định cấu hình cho các đầu ra sau:

- clk_out1: 75 MHz (đồng hồ pixel)

- clk_out2: 150 MHz (đồng hồ luồng)

- clk_out3: 50 MHz (đồng hồ axi-lite)

- Kết nối các khối video như trong hình ảnh thiết kế khối RX.

- Sau đó, chạy tự động hóa kết nối, sẽ thêm các khối AXI Interconnect, AXI SmartConnect và System Reset và cố gắng tạo các kết nối thích hợp. Đi chậm ở đây để đảm bảo rằng nó không thực hiện các kết nối không mong muốn.

- Đặt đồng hồ HDMI TMDS và chân dữ liệu bên ngoài trên khối rgb2dvi

- Không cần tín hiệu phích cắm nóng trên thiết kế này.

Bước 3: Thiết lập trình điều khiển VDMA

Việc thiết lập cho các khối khác nhau được cấu hình thông qua giao diện AXI-Lite được thực hiện tốt nhất bằng cách sử dụng các dự án demo đi kèm với BSP làm tài liệu tham khảo. Sau khi xuất phần cứng thiết kế và khởi chạy SDK từ Vivado, bạn sẽ muốn thêm gói hỗ trợ bảng mới và bao gồm thư viện lwip202 trên cửa sổ cài đặt BSP. Mở tệp tệp system.mss từ BSP và bạn sẽ thấy các trình điều khiển ngoại vi hiện diện từ thiết kế khối của bạn. Tùy chọn "Nhập ví dụ" cho phép bạn nhập các dự án demo sử dụng các thiết bị ngoại vi này và do đó chỉ cho bạn cách định cấu hình chúng trong phần mềm bằng cách sử dụng trình điều khiển Xilinx có sẵn (xem hình ảnh đính kèm).

Đây là phương pháp được sử dụng để định cấu hình VDMA, Bộ hẹn giờ & Ngắt và GPIO. Mã nguồn cho cả truyền và nhận đã được bao gồm ở đây. Sự khác biệt hầu như chỉ nằm ở main.c.

*** LƯU Ý: Vì hệ thống không hoạt động đầy đủ tại thời điểm viết bài hướng dẫn này, nên mã nguồn trong phần này không bao gồm mã mạng không dây. Một số lỗi cần được giải quyết do kết hợp các dự án truyền / nhận lõi video với các dự án truyền / nhận mạng. Do đó, hướng dẫn này xử lý chúng một cách riêng biệt trong thời điểm hiện tại. ***

Hàm xử lý ngắt TX (IRQHandler)

Chức năng này đọc các mã màu xám được cung cấp bởi cả VDMA đọc và ghi thông qua các khối GPIO. Các mã màu xám được chuyển đổi thành số thập phân và được sử dụng để chọn vị trí bộ nhớ cơ sở khung của khung hiện tại. Khung được sao chép là khung trước đó đến khung được ghi bởi VDMA (ví dụ: nếu VDMA đang ghi vào khung 2, chúng tôi sao chép khung 1; nếu ghi vào khung 0, chúng tôi quấn và đọc từ khung 2).

Chức năng chỉ chụp mỗi khung hình thứ 6 để giảm tốc độ khung hình xuống 10 Hz thay vì 60 Hz. Giới hạn trên của mạng là 300 Mbps. Ở tốc độ 10 khung hình / giây, yêu cầu băng thông 221,2 Mbps.

Nhận xét / hủy nhận xét hai dòng trong chức năng này sẽ cho phép người dùng thay đổi sang chế độ truyền qua HDMI cho mục đích gỡ lỗi / kiểm tra (mã được nhận xét để chỉ ra các dòng thích hợp). Nó hiện đang sao chép khung vào một vị trí bộ nhớ được sử dụng bởi mã ethernet.

Chức năng xử lý ngắt RX (IRQHandler)

Hàm này rất giống với hàm TX, nhưng nó sao chép từ 2 bộ đệm FIFO được ethernet sử dụng để ghi dữ liệu đến. Mã ethernet cho biết khung nào đang được ghi vào FIFO, dữ liệu được sao chép từ khung đối diện. Dữ liệu được sao chép vào khung ngay sau khung được VDMA đọc để tránh bị rách.

Bước 4: Thiết lập mạng Nanorouter

Để tạo mạng bằng bộ định tuyến nano TPlink, hãy bật nguồn riêng cho chúng và kết nối với SSID wifi mặc định cho các thiết bị. Có thể tìm thấy thêm thông tin về cài đặt cấu hình cho thiết bị cụ thể này thông qua hướng dẫn sử dụng thiết bị.

Thiết lập một trong các thiết bị làm điểm truy cập, thiết bị này sẽ hoạt động như kết nối chính cho mạng. Đảm bảo đặt tên cho mạng và ghi chú tên, đồng thời tắt DHCP (chúng tôi không muốn bộ định tuyến định cấu hình động địa chỉ IP, chúng tôi muốn bảng Zybo phát và nhận tự đặt địa chỉ IP của chúng để chúng nhất quán). Sau khi cấu hình, hãy đảm bảo thiết bị khởi động lại và thiết lập mạng này.

Thiết lập thiết bị khác làm máy khách và đảm bảo thiết bị đó kết nối với SSID mạng mà bạn thiết lập với máy tính nano đầu tiên. Một lần nữa, hãy đảm bảo rằng DHCP đã được tắt cho máy khách.

Sau khi hoàn tất và khởi động lại máy khách, nó sẽ kết nối với máy tính nano điểm truy cập (nếu không, có thể có sự cố trong cấu hình của một trong các thiết bị của bạn). Bạn sẽ nhận thấy rằng đèn LED trên máy khách sẽ sáng rõ khi nó đã kết nối với điểm truy cập.

Đèn LED của máy tính nano của điểm truy cập có thể sẽ tiếp tục nhấp nháy vào thời điểm này, điều này không sao cả! Đèn nhấp nháy có nghĩa là nó không được kết nối với thiết bị khác từ cổng ethernet của nó và khi nó được kết nối với Zybo đã được định cấu hình, đèn LED sẽ vẫn sáng cho biết kết nối mạng thành công.

Bây giờ chúng tôi đã thiết lập bộ định tuyến nano, chúng tôi có một mạng không dây cho phép chúng tôi giao tiếp thông qua. Một lưu ý quan trọng là phương pháp cấu hình của chúng tôi cho bộ định tuyến nano (như điểm truy cập và máy khách) cho phép chúng tôi giao tiếp từ bảng Zybo truyền đến bảng Zybo nhận như thể cả hai được kết nối bằng một dây ethernet. Điều này làm cho việc thiết lập mạng của chúng tôi ít khó khăn hơn, vì giải pháp thay thế có thể sẽ kết hợp việc định cấu hình bo mạch Zybo để kết nối với máy chủ một cách rõ ràng cùng với kết nối dự định.

Sau khi cả hai thiết bị được thiết lập, bộ định tuyến nano được định cấu hình và sẵn sàng triển khai vào mạng WIDI của bạn. Không có ghép nối cụ thể giữa bộ định tuyến nano và bo mạch Zybo, vì điểm truy cập hoặc máy khách sẽ hoạt động cho thiết bị truyền hoặc nhận.

Bước 5: Thiết lập hệ thống xử lý Zynq để truyền dữ liệu qua Ethernet

Để truyền dữ liệu HDMI từ bo mạch Zybo này sang bo mạch Zybo khác, chúng ta phải kết hợp giao thức Ethernet với trình điều khiển VDMA của mình. Mục tiêu của chúng tôi ở đây là truyền các khung video riêng lẻ thông qua thiết bị ngoại vi Ethernet trong hệ thống xử lý, với tốc độ đặt phù hợp với băng thông mạng của chúng tôi. Đối với dự án của chúng tôi, chúng tôi đã sử dụng TCP được cung cấp bởi API LwIP kim loại trần. Vì cả hai thành viên của dự án đều tương đối thiếu kinh nghiệm với các tiện ích mạng, lựa chọn này được đưa ra mà không nhận ra đầy đủ các tác động và ràng buộc liên quan đến TCP. Vấn đề chính với việc triển khai này là băng thông hạn chế và thực tế là nó thực sự không được thiết kế cho mục đích hấp thụ khối lượng lớn dữ liệu. Các giải pháp thay thế để thay thế TCP và cải thiện tbe trong dự án này sẽ được thảo luận sau.

Mô tả ngắn gọn về TCP với LwIP: Dữ liệu được gửi qua mạng dưới dạng gói có kích thước tcp_mss (kích thước phân đoạn tối đa của TCP), thường là 1460 byte. Việc gọi tcp_write sẽ lấy một số dữ liệu được tham chiếu bởi một con trỏ và cấu hình pbufs (bộ đệm gói) để giữ dữ liệu và cung cấp cấu trúc cho các hoạt động TCP. Số lượng dữ liệu tối đa có thể được xếp hàng đợi tại một thời điểm được đặt là tcp_snd_buf (không gian bộ đệm người gửi TCP). Vì tham số này là một số 16 bit, chúng tôi bị giới hạn ở kích thước bộ đệm gửi là 59695 byte (có một số đệm bắt buộc trong bộ đệm gửi). Khi dữ liệu đã được xếp hàng đợi, tcp_output được gọi để bắt đầu truyền dữ liệu. Trước khi gửi phân đoạn dữ liệu tiếp theo, điều bắt buộc là tất cả các gói trước đó đã được truyền thành công. Quá trình này được thực hiện bằng cách sử dụng hàm recv_callback, vì đây là hàm được gọi khi xác nhận được nhìn thấy từ bộ thu.

Việc sử dụng các dự án mẫu trong Vivado SDK rất hữu ích để tìm hiểu cách thức hoạt động của LwIP TCP và là điểm khởi đầu tốt để bắt đầu một dự án mới.

Quy trình cho thiết bị truyền WiDi như sau:

- Khởi tạo mạng TCP bằng các lệnh gọi hàm trình điều khiển LWIP kim loại trần.

- Chỉ định bất kỳ chức năng gọi lại nào cần thiết cho các hoạt động mạng.

- Kết nối với bộ thu WiDi bằng cách kết nối với địa chỉ IP và cổng của nó (cấu hình của chúng tôi: IP bộ thu là 192.168.0.9, kết nối với cổng 7).

- Khi bộ hẹn giờ trình điều khiển VDMA hết hạn, hãy nhập TX ISR.

- Xác định bộ đệm khung hiện tại để truy cập dựa trên mã màu xám VDMA

- Xếp hàng đợi phân đoạn dữ liệu đầu tiên trong bộ đệm gửi TCP

- Xuất dữ liệu và cập nhật các biến cục bộ để theo dõi lượng dữ liệu đã được gửi của khung hiện tại.

- Khi đạt đến lệnh gọi lại đã nhận (lệnh gọi hàm được thực hiện sau khi máy phát nhận được thông báo truy xuất dữ liệu), xếp hàng đợi phân đoạn dữ liệu tiếp theo.

- Lặp lại các bước 7 và 8 cho đến khi toàn bộ khung đã được gửi đi.

- Trở lại trạng thái nhàn rỗi để chờ ngắt bộ định thời tiếp theo để cho biết một khung mới đã sẵn sàng (Quay lại bước 4).

Đảm bảo thiết lập cài đặt LwIP gói hỗ trợ bo mạch như trong hình trên. Tất cả các giá trị là mặc định ngoại trừ tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Cũng lưu ý rằng có thể thực hiện gỡ lỗi chi tiết bằng cách thay đổi các tham số BSP cho nhóm debug_options.

Bước 6: Thiết lập hệ thống xử lý Zynq để tiếp nhận dữ liệu qua Ethernet

Bảng phát triển Zybo sẽ hoạt động như bộ thu không dây sẽ hoạt động tương tự như thiết bị truyền. Cài đặt gói hỗ trợ bo mạch cho LwIP sẽ giống với cài đặt trong bước trước.

Thiết bị sẽ nhận các gói chứa các phân đoạn khung hình video từ máy tính nano và nó sẽ sao chép dữ liệu khung hình video vào không gian bộ đệm khung hình ba cho VDMA nhận. Để tránh ghi đè lên bất kỳ dữ liệu nào, bộ đệm dữ liệu kép (chúng tôi sẽ gọi là bộ đệm mạng) được sử dụng khi thu thập dữ liệu từ máy tính nano, để lưu lượng mạng có thể tiếp tục phát trực tuyến trong khi khung video đầy đủ trước đó đang được sao chép vào Bộ đệm VDMA.

Quy trình đối với thiết bị nhận WiDi yêu cầu hai tác vụ, một trong số đó là nhận dữ liệu ethernet và tác vụ còn lại là sao chép các khung hình video từ bộ đệm mạng sang bộ đệm ba khung của VDMA.

Nhiệm vụ tiếp nhận Ethernet:

- Khởi tạo mạng TCP bằng cách gọi hàm trình điều khiển LWIP kim loại trần (thiết lập với địa chỉ IP mà bộ phát sẽ kết nối, 192.168.0.9 của chúng tôi)

- Chỉ định bất kỳ chức năng gọi lại nào cần thiết cho các hoạt động mạng.

- Khi nhận được gói ethernet, hãy sao chép dữ liệu gói vào bộ đệm mạng hiện tại, tăng dữ liệu tích lũy hiện tại.

- Nếu gói lấp đầy bộ đệm khung mạng, hãy tiếp tục đến bước 5 & 6. Nếu không, hãy lặp lại bước 3 cho tác vụ này.

- tín hiệu rằng tác vụ bộ đệm ba khung VDMA nên sao chép từ bộ đệm mạng mới hoàn thành.

- Chuyển sang bộ đệm mạng khác và tiếp tục thu thập dữ liệu qua ethernet.

- Chờ cho đến khi nhận được gói ethernet mới (bước 3).

Sao chép bộ đệm mạng sang bộ đệm ba khung VDMA:

- Khi bộ hẹn giờ trình điều khiển VDMA hết hạn, hãy nhập RX ISR.

- Xác định bộ đệm khung hiện tại để truy cập dựa trên mã màu xám VDMA.

- Xác định bộ đệm mạng nào sẽ được sao chép vào bộ đệm VDMA và sao chép dữ liệu đó

Bước 7: Kết nối các bo mạch Zybo của bạn với Nguồn HDMI và Ổ cắm HDMI

Bây giờ kết nối cáp hdmi cho cả bộ thu và bộ phát, lập trình FPGA và chạy hệ thống xử lý. Tốc độ khung hình có thể sẽ rất chậm, do chi phí lớn trong hoạt động LwIP và băng thông hạn chế. Nếu có bất kỳ sự cố nào, hãy kết nối qua UART và cố gắng xác định bất kỳ cảnh báo hoặc lỗi nào.

Bước 8: Ý tưởng thay thế để cải tiến

Một vấn đề lớn đối với dự án này là lượng dữ liệu cần thiết để gửi qua wifi. Điều này đã được mong đợi, tuy nhiên, chúng tôi đã đánh giá thấp tác động của điều này và dẫn đến nhiều loạt hình ảnh trên màn hình hơn là nguồn cấp dữ liệu video. Có một số cách để cải thiện dự án này:

- Nén video thời gian thực. Việc nén từng khung hình nguồn cấp dữ liệu video đến sẽ làm giảm đáng kể lượng dữ liệu cần được gửi qua mạng. Lý tưởng nhất là điều này sẽ được thực hiện trong phần cứng (đây không phải là một nhiệm vụ dễ dàng) hoặc nó có thể được thực hiện trong phần mềm bằng cách sử dụng lõi ARM khác để chạy các thuật toán nén (điều này sẽ cần một số phân tích thêm để đảm bảo thời gian hoạt động). Có một số thành phần nén video thời gian thực nguồn mở mà chúng tôi tìm thấy trên web, nhưng phần lớn là IP.

- Triển khai luồng Ethernet trong phần cứng, thay vì phần mềm. Có rất nhiều chi phí do thiếu không gian có sẵn để xếp hàng dữ liệu gửi đi trong máy phát, do giới hạn về kích thước phân đoạn. Một quy trình hiệu quả hơn nhiều là sử dụng AXI Ethernet IP với bộ đệm FIFO hoặc DMA để cấp dữ liệu vào đó. Điều này sẽ giảm bớt hành lý thừa từ LwIP TCP và cho phép nhiều luồng dữ liệu hơn.

Bước 9: Khả năng tiếp cận

Sản phẩm kết quả của dự án WiDi này phải là một cặp thiết bị nhỏ gọn, tích hợp đầy đủ mà người dùng có thể kết nối với bất kỳ nguồn HDMI nào và sau đó đưa nguồn cấp dữ liệu video vào màn hình có khả năng HDMI không dây. Các thiết bị này sẽ có Zynq-7000 SoC được tìm thấy trên bo mạch tham chiếu Zybo và kết hợp phần cứng mạng có trong bộ định tuyến nano TP-Link. Lý tưởng nhất là người dùng có thể điều khiển mô-đun truyền từ một vị trí riêng biệt trong hệ điều hành mục tiêu mà không cần nhiều khả năng kỹ thuật đáng kể.

Bảo mật và kết nối

Các thiết bị cũng phải kết hợp Bảo mật tầng truyền tải (TLS) và có khả năng tự động kết nối hạn chế, cho cả mục đích bảo mật. Ý định của các nhà thiết kế là làm cho việc kết nối với màn hình hiển thị qua giao diện không dây là một hành động có chủ ý thay mặt người dùng để tránh phát nhầm nội dung nhạy cảm.

Hiện trạng

Cho đến thời điểm này, tình trạng của dự án vẫn là một công việc đang được hoàn thiện. Để người dùng điểm cuối hiện tại được hưởng lợi từ hướng dẫn này, họ phải có hiểu biết kỹ thuật vững chắc về thiết kế hệ thống nhúng và phải quen thuộc với phần cứng có thể lập trình và phần mềm nhúng hoạt động cùng nhau.

Tại thời điểm này, dữ liệu được gửi qua mạng không được mã hóa và được coi là truyền thô các gói TCP / IP.

Dự án lõi video đã được thử nghiệm thành công cho cả truyền và nhận. Mặt khác, kết nối không dây giữa hai bo mạch zybo đã được thiết lập và dữ liệu khung thử nghiệm đã được gửi thành công. Tuy nhiên, vẫn cần thiết phải kết hợp mã mạng cho từng dự án lõi video và kiểm tra việc truyền các khung video thực tế.

Đề xuất:

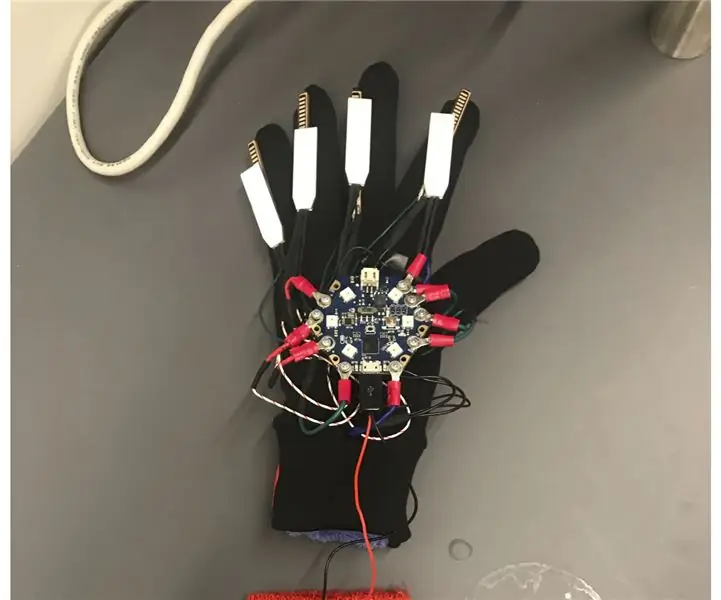

Làm thế nào để tạo ra một chiếc găng tay không dây cho đàn piano không dây: 9 bước

Cách tạo găng tay piano không dây: Mục đích và chức năng: Dự án công nghệ có thể đeo của chúng tôi là tạo ra găng tay piano không dây với đèn đồng bộ bằng cách sử dụng thiết bị điện tử cơ bản, bộ điều khiển vi mô như HexWear và máy tính xách tay với phần mềm Arduino và Max 8 . Việc sử dụng proj của chúng tôi

Robot Arduino không dây sử dụng mô-đun không dây HC12: 7 bước

Robot Arduino không dây sử dụng mô-đun không dây HC12: Xin chào các bạn, chào mừng trở lại. Trong bài trước của tôi, tôi đã giải thích về Mạch cầu H là gì, IC điều khiển động cơ L293D, IC điều khiển động cơ L293D để điều khiển các trình điều khiển động cơ cao cấp và cách bạn có thể thiết kế và tạo Bảng điều khiển động cơ L293D của riêng mình,

Điểm truy cập không dây phạm vi 50 mét với bộ điều hợp không dây USB TP Link WN7200ND trên Raspbian Stretch: 6 bước

Điểm truy cập không dây phạm vi 50 mét với Bộ điều hợp không dây USB TP Link WN7200ND trên Raspbian Stretch: Raspberry Pi rất tuyệt để tạo Điểm truy cập không dây an toàn nhưng nó không có phạm vi tốt, tôi đã sử dụng Bộ điều hợp không dây USB TP Link WN7200ND để mở rộng nó. Tôi muốn chia sẻ cách thực hiện Tại sao tôi muốn sử dụng raspberry pi thay vì bộ định tuyến? T

Quấn dây gọn gàng mà không có dây buộc hoặc rối: 5 bước (có hình ảnh)

Quấn dây gọn gàng mà không cần dây buộc hoặc rối: Mục tiêu: một cách để quấn dây (tai nghe, nguồn điện, v.v.) mà không cần dây buộc hoặc dây Velcro, nhanh chóng, không bị hoàn tác và nhanh chóng hoàn tác. Đây là một phương pháp, bất kỳ đề xuất nào tốt hơn? Hướng dẫn khác: http://www.curiousinventor.com/guidesVideo showi

Xây dựng bộ điều khiển máy ảnh không dây đa chức năng (giá rẻ!) Của riêng bạn.: 22 bước (có hình ảnh)

Tự chế bộ điều khiển máy ảnh không dây đa chức năng (giá rẻ!): Giới thiệu Bạn đã bao giờ thích xây dựng bộ điều khiển máy ảnh của riêng mình chưa? QUAN TRỌNG LƯU Ý: Tụ điện cho MAX619 là 470n hoặc 0,47u. Giản đồ đúng, nhưng danh sách thành phần bị sai - được cập nhật. Đây là một mục vào Digital Da