Mục lục:

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:31.

- Sửa đổi lần cuối 2025-01-23 15:15.

Trong Tài liệu hướng dẫn này, chúng tôi sẽ mô tả cách triển khai bộ chuyển đổi tương tự-kỹ thuật số (ADC) 8 bit trong SLG46855V có thể cảm nhận dòng điện tải và giao tiếp với MCU thông qua I2C. Thiết kế này có thể được sử dụng cho các ứng dụng cảm biến hiện tại khác nhau như ampe kế, hệ thống phát hiện lỗi và đồng hồ đo nhiên liệu.

Dưới đây, chúng tôi mô tả các bước cần thiết để hiểu cách giải pháp đã được lập trình để tạo ra cảm giác hiện tại của ADC. Tuy nhiên, nếu bạn chỉ muốn lấy kết quả của việc lập trình, hãy tải phần mềm GreenPAK để xem File thiết kế GreenPAK đã hoàn thành. Cắm Bộ phát triển GreenPAK vào máy tính của bạn và nhấn chương trình để tạo cảm giác hiện tại của ADC.

Bước 1: Kiến trúc ADC

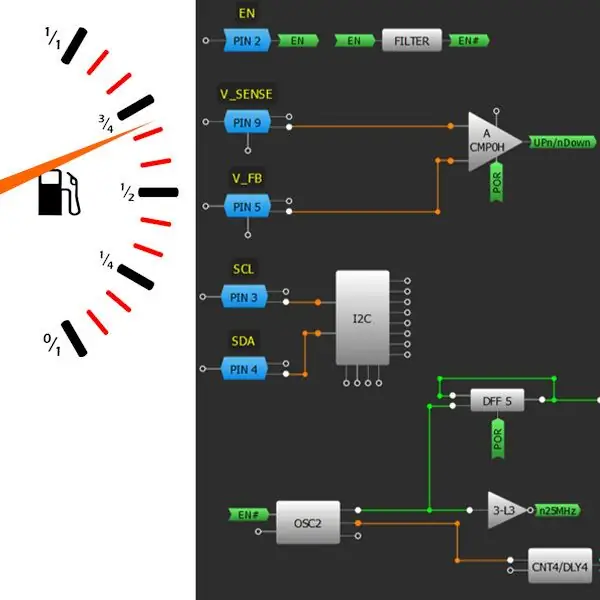

ADC về cơ bản bao gồm một bộ so sánh tương tự và một Bộ chuyển đổi kỹ thuật số sang tương tự (DAC). Bộ so sánh cảm nhận điện áp đầu vào so với điện áp đầu ra DAC, và sau đó điều khiển xem tăng hay giảm mã đầu vào DAC, sao cho đầu ra DAC hội tụ với điện áp đầu vào. Mã đầu vào DAC kết quả trở thành mã đầu ra kỹ thuật số ADC.

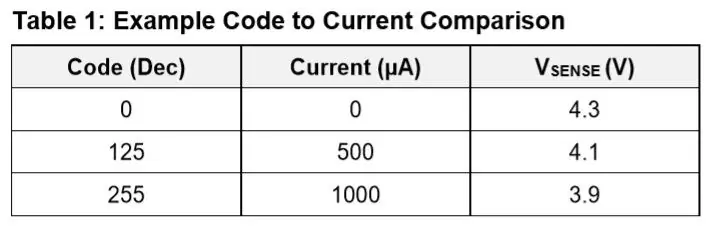

Trong quá trình thực hiện, chúng tôi tạo một DAC bằng cách sử dụng mạng điện trở điều khiển độ rộng xung (PWM). Chúng tôi có thể dễ dàng tạo ra một đầu ra PWM được điều khiển kỹ thuật số chính xác bằng cách sử dụng GreenPAK. PWM khi được lọc sẽ trở thành điện áp tương tự của chúng ta và do đó đóng vai trò như một DAC hiệu quả. Một ưu điểm khác biệt của phương pháp này là dễ dàng đặt điện áp tương ứng với mã 0 và thang đo đầy đủ (bù và khuếch đại tương đương) bằng cách điều chỉnh đơn giản các giá trị điện trở. Ví dụ: người dùng muốn đọc mã 0 một cách lý tưởng từ cảm biến nhiệt độ không có dòng điện (0 µA) tương ứng với 4,3 V và mã toàn thang ở 1000 µA tương ứng với 3,9 V (Bảng 1). Điều này có thể dễ dàng thực hiện bằng cách chỉ cần thiết lập một vài giá trị điện trở. Bằng cách để phạm vi ADC phù hợp với phạm vi cảm biến quan tâm, chúng tôi tận dụng tối đa độ phân giải ADC.

Cân nhắc thiết kế cho kiến trúc này là tần số PWM nội bộ cần nhanh hơn nhiều so với tốc độ cập nhật ADC để ngăn chặn hành vi bị cản trở của vòng điều khiển của nó. Ít nhất nó phải dài hơn đồng hồ bộ đếm dữ liệu ADC chia cho 256. Trong thiết kế này, khoảng thời gian cập nhật ADC được đặt thành 1,3312 ms.

Bước 2: Mạch bên trong

ADC linh hoạt dựa trên thiết kế được trình bày trong Dialog Semiconductor AN-1177. Tốc độ xung nhịp được tăng từ 1 MHz lên 12,5 MHz để tạo xung nhịp cho bộ đếm ADC vì SLG46855 có sẵn xung nhịp 25 MHz. Điều này cho phép tốc độ cập nhật nhanh hơn nhiều để có độ phân giải mẫu tốt hơn. Đồng hồ LUT xung nhịp dữ liệu ADC được thay đổi vì vậy nó sẽ đi qua tín hiệu 12,5 MHz khi PWM DFF ở mức thấp.

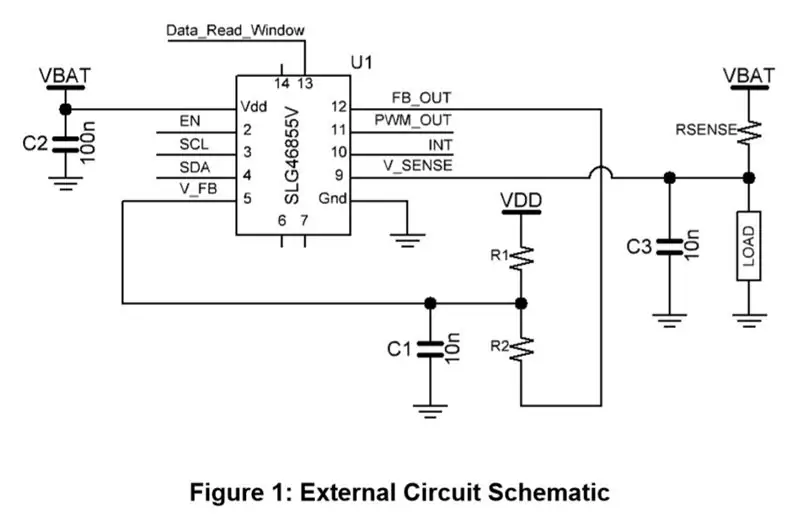

Bước 3: Mạch bên ngoài

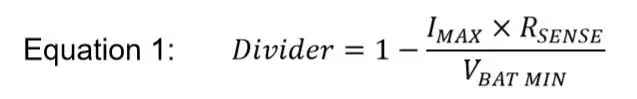

Mạng điện trở và tụ điện bên ngoài được sử dụng để chuyển đổi PWM thành điện áp tương tự như trong sơ đồ mạch ở Hình 1. Các giá trị được tính toán cho độ phân giải tối đa đối với dòng điện lớn nhất mà thiết bị sẽ cảm nhận được. Để đạt được tính linh hoạt này, chúng tôi thêm điện trở R1 và R2 song song với VDD và nối đất. Một bộ chia điện trở chia VBAT xuống phía thấp của dải điện áp. Tỷ lệ bộ chia cho một VBAT tối thiểu dự kiến có thể được giải quyết bằng cách sử dụng phương trình 1.

Bước 4: I2C Đọc hướng dẫn

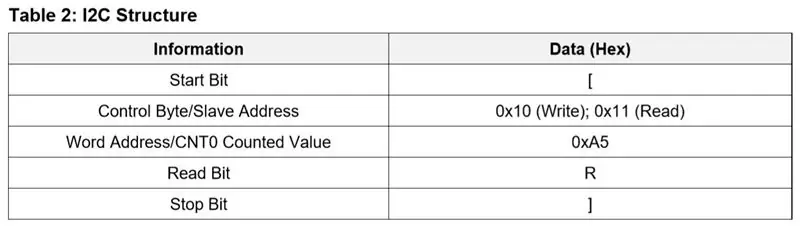

Bảng 1 mô tả cấu trúc lệnh I2C để đọc lại dữ liệu được lưu trữ trong CNT0. Các lệnh I2C yêu cầu một bit bắt đầu, byte điều khiển, địa chỉ từ, bit đọc và bit dừng.

Một lệnh I2C ví dụ để đọc lại giá trị được đếm CNT0 được viết dưới đây:

[0x10 0xA5] [0x11 R]

Giá trị đếm được đọc lại sẽ là giá trị mã ADC. Ví dụ: mã Arduino được bao gồm trong tệp ZIP của ghi chú ứng dụng này trên trang web của Dialog.

Bước 5: Kết quả

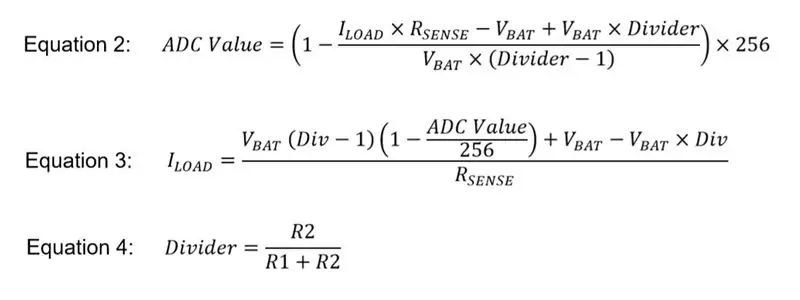

Để kiểm tra độ chính xác của thiết kế cảm biến dòng ADC, các giá trị đo được ở mức dòng tải và VDD nhất định được so sánh với giá trị lý thuyết. Giá trị ADC lý thuyết được tính theo công thức 2.

ILOAD tương quan với giá trị ADC được tìm thấy trong phương trình 3.

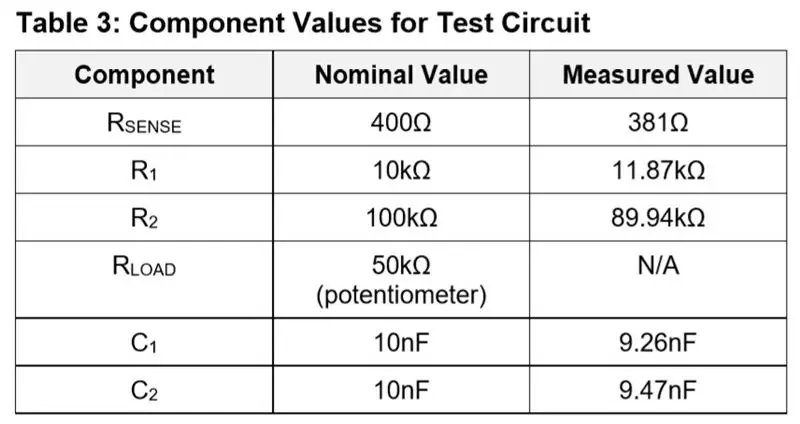

Đối với các kết quả sau, tôi đã sử dụng các giá trị thành phần này được hiển thị trong Bảng 3.

Độ phân giải của giá trị ADC thành chuyển đổi ILOAD có thể được tính bằng cách sử dụng phương trình 3 với các giá trị đo được trong Bảng 2 và giá trị ADC được đặt thành 1. Với VBAT là 3,9 V, độ phân giải là 4,96 µA / div.

Để tối ưu hóa mạch cảm nhận dòng ADC đến mức VDD tối thiểu là 3,6 V với dòng điện tối đa là 1100 µA và điện trở cảm nhận 381 Ω, hệ số phân chia lý tưởng sẽ là 0,884, dựa trên phương trình 1. Với các giá trị cho trong Bảng 2, dải phân cách thực tế có hệ số chia là 0,876. Vì điều này nhỏ hơn một chút, nó sẽ cho phép phạm vi dòng tải lớn hơn một chút để các giá trị ADC gần với phạm vi đầy đủ nhưng sẽ không bị tràn. Giá trị bộ chia thực tế được tính theo công thức 4.

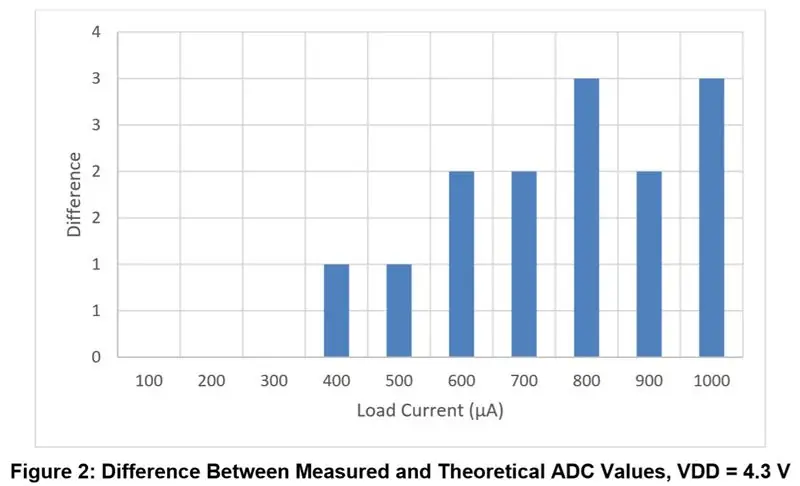

Trên đây (Hình 2-6, Bảng 4-6) là các phép đo được thực hiện của mạch ở ba mức điện áp: 4,3 V, 3,9 V và 3,6 V. Mỗi mức hiển thị một biểu đồ hiển thị sự khác biệt giữa giá trị ADC đo được và lý thuyết. Các giá trị lý thuyết được làm tròn thành số nguyên gần nhất. Có một đồ thị tóm tắt để so sánh sự khác biệt ở ba cấp điện áp. Sau đó, có một đồ thị hiển thị mối tương quan giữa các giá trị ADC lý thuyết và dòng tải ở các mức điện áp khác nhau.

Phần kết luận

Thiết bị đã được thử nghiệm ở ba mức điện áp: 3,6 V, 3,9 V và 4,3 V. Phạm vi điện áp này mô hình hóa pin lithium ion đầy đủ phóng điện đến mức danh định. Trong số ba mức điện áp, thiết bị thường chính xác hơn ở mức 3,9 V đối với mạch bên ngoài đã chọn. Sự khác biệt giữa các giá trị ADC đo được và lý thuyết chỉ là 1 giá trị thập phân tắt ở dòng tải 700 - 1000 µA. Tại dải điện áp đã cho, các giá trị ADC đo được cao hơn 3 điểm thập phân so với điều kiện danh định trong trường hợp xấu nhất. Có thể điều chỉnh thêm bộ chia điện trở để tối ưu hóa các mức điện áp VDD khác nhau.

Đề xuất:

Giá đỡ phím giắc cắm ghi-ta Arduino với nhận dạng giắc cắm & OLED: 7 bước

Arduino Guitar Jack Key Holder With Jack Recognition & OLED: Giới thiệu: Hướng dẫn này sẽ trình bày chi tiết việc xây dựng chủ key plugin Guitar Jack dựa trên Arduino của tôi

Sửa giắc cắm tai nghe bị hỏng của bạn: 5 bước

Sửa giắc cắm tai nghe bị hỏng: Âm nhạc dành cho tất cả mọi người và trong những năm qua, âm nhạc ngày càng trở nên dễ tiếp cận hơn trên các thiết bị khác nhau như iPod, Điện thoại, v.v. Và cách phổ biến nhất để nghe nhạc là sử dụng tai nghe và thưởng thức âm nhạc và hầu hết các tai nghe đều sử dụng một

Cách vệ sinh giắc cắm tai nghe 1/8 "(3,5 mm): 6 bước

Cách vệ sinh giắc cắm tai nghe 1/8 "(3,5 mm): Cách vệ sinh giắc cắm tai nghe phổ biến trên hầu hết các thiết bị di động. Giắc cắm 1/8 " được tìm thấy trên hầu hết các thiết bị di động (và với sự gia tăng của iPod, có hàng triệu của các giắc cắm như vậy). Có tính di động, giắc cắm tiếp xúc với rất nhiều

Giắc cắm giắc cắm tai nghe iPhone của Apple: 7 bước

Giắc cắm giắc cắm tai nghe iPhone của Apple: Giắc cắm tai nghe trên iPhone của Apple đã bị ảnh hưởng rất nhiều vì nó không hoạt động với hầu hết các tai nghe tiêu chuẩn vì nó bị lõm xuống. Sự khó chịu rõ ràng đó đã che giấu một nhược điểm quan trọng khác đối với thiết kế giắc cắm tai nghe - đó là

Cách khắc phục sự cố giắc cắm tai nghe trên Slacker G2: 5 bước

Cách khắc phục sự cố giắc cắm tai nghe trên Slacker G2: Xin chào, Đây là hướng dẫn về cách sửa lỗi giắc cắm tai nghe khó chịu trên Slacker G2.Mic liên tục cắt vào và ra, và bật ra! Rất khó chịu! Vấn đề rất phổ biến, tôi đã phải tự mình sửa Slacker của mình, vì Slacker sẽ không thay thế nó. Grrrrrr.Vì vậy, đây là