Mục lục:

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:30.

- Sửa đổi lần cuối 2025-01-23 15:14.

JDM là một lập trình PIC phổ biến vì nó sử dụng một cổng nối tiếp, tối thiểu các thành phần và không cần nguồn điện. Nhưng có sự nhầm lẫn ở đó, với nhiều biến thể lập trình viên trên mạng, cái nào làm việc với PIC nào? Trong phần "có thể hướng dẫn" này, chúng tôi đưa JDM vào thử nghiệm và tôi trình bày cách mô phỏng mạch bằng Spice sẽ trả lời tất cả các câu hỏi của bạn!

Quân nhu

LTspice có thể được tải xuống từ Thiết bị Analog tại đây.

Bạn cũng cần các tệp mạch JDM ở đây.

Bước 1: Yêu cầu về cổng nối tiếp

JDM yêu cầu một cổng nối tiếp đáp ứng thông số kỹ thuật EIA232, lý tưởng là với các mức Điện áp + 12 / -12.

Theo bảng dữ liệu MC1488 của Texas Instruments Line Driver (Hình 3)

Trở kháng đầu ra = 4V / 8mA = 500 ohm.

Dòng ngắn mạch giới hạn = 12mV, không giới hạn thời gian - không làm hỏng chip.

Trở kháng đầu vào của máy thu đường dây = 3k đến 7k ohm được khuyến nghị.

Cổng nối tiếp trên máy tính để bàn cũ hơn sử dụng + 12v / -12V đáp ứng yêu cầu này.

Cổng nối tiếp trên máy tính xách tay mới hơn sử dụng điện áp thấp hơn. JDM có thể hoạt động hoặc không - câu trả lời phức tạp hơn.

Bước 2: Yêu cầu lập trình PIC

Thông tin liên quan đến các yêu cầu lập trình PIC được lấy từ Microchip. Trên đây là cho một thiết bị điển hình.

Bước 3: Đặc điểm kỹ thuật JDM

Trang web JDM ban đầu có bị mất trong sương thời gian không? Điều này khiến chúng tôi đoán những gì nhà thiết kế dự định ban đầu cho đặc điểm kỹ thuật.

- Cung cấp VDD = 5V và tối đa lên đến IDD = 2mA (đối với phiên bản "trong ổ cắm")

- Cung cấp VHH = 13V và đến cực đại IHH = 0,2mA.

- MCLR Thời gian tăng tVHHR = 1uS max.

- Phiên bản ICSP phải có khả năng kéo MCLR xuống thấp so với mức kéo lên 22k trên mục tiêu.

Bước 4: Mô tả mạch

Hình JDM1 dựa trên mạch JDM “tiêu chuẩn” lấy từ trang web PICPgm. Đây là bộ lập trình “PIC in Socket” nơi PIC lấy nguồn từ các chân TX và RTS. Sơ đồ ban đầu rất khó hiểu vì vậy tôi đã vẽ lại nó bằng cách sử dụng quy ước thông thường của dòng điện từ trên xuống dưới. Và tôi đã thêm các chỉ báo LED “RESET”, “PROG” và “RTS” cần thiết trong quá trình xây dựng và thử nghiệm. Hy vọng rằng những điều này không có bất kỳ ảnh hưởng bất lợi cho hành vi.

Quy ước bình thường của thiết kế mạch là chung cho tất cả các cơ sở, nhưng đặc điểm chính của JDM là mặt đất cổng nối tiếp (GND) được kết nối với VDD. Điều này tạo ra sự nhầm lẫn vì tín hiệu cổng nối tiếp được đo đối với tín hiệu GND, PIC đối với mặt đất logic (VSS).

Khi TX tăng cao, Q1 hoạt động như hai điốt phân cực thuận. (Bộ thu Q1 không được phân cực ngược như với hoạt động của bóng bán dẫn bình thường). Bộ thu Q1 sạc C2, được kẹp ở VDD + 8V bởi Zener (D3). Bộ phát Q1 phân phối 13V đến MCLR cho Chế độ Chương trình / Xác minh.

Khi TX xuống mức thấp, tụ điện C3 được sạc qua D1 và VSS được kẹp ở VDD-5V bởi zener (D5). Ngoài ra TX được kẹp ở (VSS-0,6) bởi D1. Q1 tắt, C1 giữ điện cho xung lập trình tiếp theo. MCLR được kẹp ở 0V bởi D2, vì vậy PIC bây giờ được Reset.

Khi RTS ở mức cao, đồng hồ được truyền tới PGC. D4 kẹp PGC ở mức logic VDD. Khi RTS ở mức thấp, tụ điện C3 được sạc qua D6 và VSS được kẹp ở VDD-5V bởi zener (D5). D6 kẹp PGC tại VSS hoặc logic 0.

Trong quá trình lập trình, dữ liệu được gửi trên DTR được đọc trên PGD, được PIC cấu hình làm đầu vào. Khi DTR cao, Q2 hoạt động như “người theo dõi bộ phát” và điện áp PGD khoảng (VDD-0,6) hoặc mức logic 1. Khi DTR thấp, Q2 hoạt động như một bóng bán dẫn xấu (chân cực phát và chân thu bị đảo ngược). Q2 kéo PGD xuống thấp, được kẹp bởi D7 tại VSS hoặc logic 0.

Trong quá trình xác minh, PIC cấu hình PGD làm đầu ra để gửi dữ liệu đến cổng nối tiếp. DTR phải được đặt cao và dữ liệu được đọc trên CTS. Khi ngõ ra PGD ở mức cao, Q2 tắt, CTS = DTR = + 12V. Khi sản lượng PGD ở mức thấp, Q2 sẽ bật. Bộ thu Q2 lấy dòng điện (12V + 5V) / (1k + 1k5) = 7mA từ DTR, và kéo CTS xuống mức thấp, đến VSS.

Bước 5: Chuẩn bị cho mô phỏng

Tải xuống LT gia vị, lưu và mở các tệp mạch (*.asc) được cung cấp tại đây. Để mô phỏng mạch, chúng ta phải cung cấp cho nó một số đầu vào, sau đó "theo dõi" các đầu ra. V1, V2 V3 mô phỏng cổng nối tiếp 12V với trở kháng đầu ra R11, R12, R13.

- V1 tạo ra 2 xung chương trình trên TX từ 0,5ms đến 4,5ms

- V2 tạo ra một loạt các xung dữ liệu trên DTR từ 1,5 đến 4,5 mili giây

- V3 tạo ra một loạt xung đồng hồ trên RTS từ 0,5 đến 3,5ms

Các thành phần V4, X1, R15 và R16 đều là một phần của mô phỏng.

- V4 tạo ra 2 xung từ 2,5 đến 4,5ms để xác minh dữ liệu.

- Jumper X1 mô phỏng OUTPUT trên PGD.

- R15, R16 mô phỏng quá trình “tải” PIC trên VDD và MCLR.

Bước 6: Sửa đổi ICSP

Hình JDM3 cho thấy phiên bản cho lập trình "trong mạch". Các sửa đổi từ bản gốc là

- Thay thế ổ cắm ZIF bằng đầu nối ICSP.

- PIC bây giờ được cấp nguồn bằng nguồn cung cấp cho mạch đích (V5).

- Loại bỏ zener 5V (D5).

- Tụ điện 100pF nhỏ (C4) được di chuyển bên cạnh PIC trên mạch mục tiêu.

- Đèn LED lấy điện từ bảng mạch nếu có thể.

- Điện trở kéo lên MCLR (R10) và diode (D10) được yêu cầu trên mạch mục tiêu.

- CẢNH BÁO. Bảng mục tiêu phải có nguồn cung cấp "nổi", lý tưởng là pin.

- Không kết nối mặt đất đích (VSS) với mặt đất máy tính / PC bằng cách kết nối bất kỳ cổng máy tính nào khác cùng lúc với JDM.

Sau khi mô phỏng JDM1, vấn đề thời gian sạc lâu trên C2 trở nên rõ ràng. Sau đó, sau khi đọc Fruttenboel, có vẻ như C2 và Q1 đã được thêm vào như một sửa đổi cho bản gốc. Tôi không thể nghĩ C2 và Q1 dự định làm gì ngoài việc tạo ra các vấn đề. Vì vậy, đối với JDM4, chúng tôi hoàn nguyên về thiết kế cũ hơn trên Fruttenboel, đơn giản và dễ hiểu. D1 và D3 / LED2 kẹp MCLR giữa VSS và VDD + 8V. Giá trị của R1 giảm đi 3k3 vừa đủ để LED2 sáng ở mức 12V.

JDM4 cũng được thiết kế để hoạt động với các cổng nối tiếp yếu hơn. Khi TX lên mức cao (+ 9V), nguồn dòng TX = (9-8) / (1k + 3k3) = 0,2ma, vừa đủ để kéo MCLR lên cao mặc dù không đủ để chiếu sáng LED2. Khi TX xuống thấp (khoảng -7V), dòng TX chìm = (9-7) / 1k = 2mA. LED1 hiện tại = (7-2 cho dẫn) / (2k7) = 1,8mA. MCLR kéo dòng xuống = 7-5,5 / 3k3 = 0,5mA.

Mạch này cũng đã được thử nghiệm (mô phỏng JDM5) để xem điều gì xảy ra với các cổng nối tiếp tối thiểu +/- 7V, nơi không đủ điện áp để duy trì VHH = 13V. Mục đích của C1 bây giờ trở nên rõ ràng, C1 tạo ra một sự thúc đẩy ngắn + ve cho MCLR, một mức tăng đột biến 33us trên cạnh tăng của TX, đủ dài để PIC vào chế độ lập trình, có lẽ? Nhưng loại bỏ jumper X2 (tắt LED1) vì không có đủ dòng điện để kéo MCLR xuống thấp và chiếu sáng LED1 cùng nhau. Khi TX xuống thấp, dòng TX chìm = (7V-5.5V) / (1k + 3k3) = 0,3mA, vừa đủ để kéo MCLR xuống thấp so với R10 kéo lên.

Bước 7: Kết quả mô phỏng

Để xem các tệp đồ họa, tốt hơn là nhấp chuột phải vào các liên kết bên dưới, sau đó chọn "Mở liên kết trong Tab Mới"

Mô phỏng 1: theo dõi MCLR, VSS và RTS cho JDM1 gốc. Ngay lập tức quan sát 1, 2 và 3 là rõ ràng.

Mô phỏng 2: theo dõi MCLR và VSS, và RTS cho JDM2 đã sửa đổi, khắc phục các sự cố trước đó.

Mô phỏng 3: theo dõi PGD, VSS và PGC để gửi dữ liệu JDM2 trong chế độ chương trình. Tầm quan sát 4 ở 3,5mS.

Mô phỏng 4: theo dõi PGD, VSS và CTS cho JDM2 trong chế độ xác minh (jumper X1 được chèn vào). VÂNG

Mô phỏng 5: theo dõi MCLR, VSS, PGD và PGC cho JDM3. ICSP sử dụng nguồn từ mạch giải quyết được nhiều vấn đề.

Mô phỏng 6: theo dõi MCLR, VSS, PGD và PGC cho JDM4 với cổng nối tiếp +/- 9V. MCLR tăng ngay lập tức, hoạt động hoàn toàn.

Mô phỏng 7: theo dõi MCLR, VSS và TX cho JDM5 với cổng nối tiếp +/- 7V và jumper X2 bị loại bỏ. C1 tạo ra một mức tăng + ve (tăng đột biến) trên cạnh tăng của MCLR, vừa đủ để đẩy MCLR trên TX đến 13V.

Bước 8: Kết luận

Spice thực sự giỏi trong việc tiết lộ "bí mật ẩn giấu" của hoạt động mạch. Rõ ràng là mạch JDM hoạt động và tương thích với nhiều chip PIC, nhưng những quan sát sau đây cho thấy những hạn chế / vấn đề / lỗi tương thích có thể xảy ra?

- Thời gian tăng MCLR dài trong khi C2 tính phí đến VPP trên xung đầu tiên của TX. Không đạt yêu cầu kỹ thuật 3.

- Cổng nối tiếp tính phí C2 khi TX tăng cao và RTS xuống thấp. Nhưng RTS cũng có nhiệm vụ sạc C3. Khi cả hai xảy ra cùng lúc, điều này tạo ra nhiều tải hơn trên RTS, do đó C3 mất điện tích (VSS tăng) ở 2ms trên mô phỏng. Không đạt yêu cầu kỹ thuật 1.

- C3 mất điện tích (VSS bắt đầu tăng) sau khi xung đồng hồ dừng ở 3,5ms.

- Mục đích của C2 là gì, nó có cần thiết không?

Các giải pháp

- Có lẽ PICPgm sử dụng một phần mềm “work-round”. Nó phải áp dụng một xung TX dài để nạp trước cho C2, sau đó chỉ vào chế độ lập trình sau xung TX thứ hai? Đối với mô phỏng, tôi đã giảm giá trị của C2 xuống 1uF để tạo ra thời gian tăng 1ms. Không phải là một giải pháp lý tưởng.

- Tách C2 và C3 để chúng tích điện độc lập. Một sửa đổi nhỏ đối với JDM2, C2 được tham chiếu đến GND thay vì VSS.

- Được giải quyết bởi JDM3. ICSP đáng tin cậy hơn nhiều vì PIC được cấp nguồn bởi mạch đích.

- JDM4 giải quyết vấn đề 1. Đây là một thiết kế đơn giản loại bỏ hoàn toàn C2.

Bước 9: Và cuối cùng

miếng bánh pudding đang bị ăn dở. JDM này hoạt động nên hãy tiếp tục sử dụng nó.

Và các đề xuất của tôi là:

- sử dụng JDM2 để lập trình ổ cắm và cổng nối tiếp 12V,

- sử dụng JDM4 cho trình lập trình ICSP và các cổng nối tiếp trên +/- 9V,

- sử dụng JDM4 với jumper X2 bị loại bỏ cho các cổng nối tiếp trên +/- 7V.

Người giới thiệu:

Thiết bị tương tự LT gia vị

picpgm

Fruttenboel

Theo dõi các dự án PIC khác tại góc tinh quái

Đề xuất:

Cách Flash hoặc Lập trình Phần mềm cơ sở ESP8266 AT bằng cách Sử dụng Bộ lưu trữ và Lập trình ESP8266, Mô-đun IOT Wifi: 6 bước

Làm thế nào để Flash hoặc lập trình Phần mềm cơ sở ESP8266 AT bằng cách sử dụng Bộ lưu trữ và lập trình ESP8266, Mô-đun Wifi IOT: Mô tả: Mô-đun này là một bộ điều hợp / lập trình USB cho các mô-đun ESP8266 thuộc loại ESP-01 hoặc ESP-01S. Nó được trang bị thuận tiện với đầu cắm cái 2x4P 2,54mm để cắm ESP01. Ngoài ra, nó phá vỡ tất cả các chân của ESP-01 thông qua một nam 2x4P 2,54mm h

(gần như) Lập trình viên MIDI SysEx CC đa năng (và Trình tự lập trình tự ): 7 bước (có Hình ảnh)

(gần như) Lập trình viên MIDI SysEx CC đa năng (và Trình lập trình …): Vào giữa những năm tám mươi, các bộ sản xuất tổng hợp bắt đầu " ít hơn là tốt hơn " quá trình dẫn đến synths barebone. Điều này cho phép giảm chi phí về mặt sản xuất, nhưng làm cho quá trình vá lỗi trở nên thành công nếu không muốn nói là không thể sử dụng cuối cùng

Lập trình vi điều khiển với bộ lập trình USBasp trong Atmel Studio: 7 bước

Lập trình vi điều khiển với một lập trình viên USBasp trong Atmel Studio: Hi Tôi đã đọc và học qua nhiều hướng dẫn dạy cách sử dụng lập trình USBasp với Arduino IDE, nhưng tôi cần sử dụng Atmel Studio để làm bài tập ở trường Đại học và không thể tìm thấy bất kỳ hướng dẫn nào. Sau khi nghiên cứu và đọc qua nhiều r

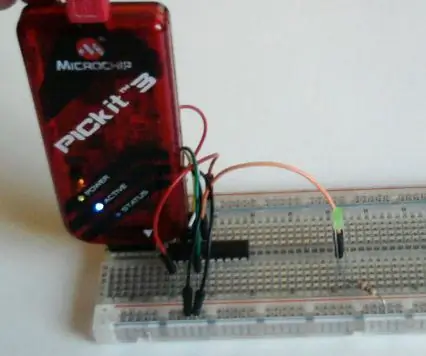

Cách lập trình MCU PIC với bộ lập trình PICkit bằng bảng mạch: 3 bước

Cách lập trình PIC MCU Với Bộ lập trình PICkit Sử dụng Bảng mạch: Bạn không cần các công cụ đắt tiền và phức tạp để chơi với các bộ vi điều khiển PIC (hoặc bất kỳ loại nào khác). Tất cả những gì bạn cần là một bảng mạch để bạn kiểm tra mạch và lập trình của mình. Tất nhiên một số loại lập trình viên và IDE là cần thiết. Trong hướng dẫn này

Hướng dẫn lập trình thú vị cho nhà thiết kế - Kiểm soát quy trình chương trình- Tuyên bố vòng lặp: 8 bước

Hướng dẫn lập trình thú vị cho nhà thiết kế - Điều khiển quy trình chương trình- Tuyên bố vòng lặp: Điều khiển quy trình chương trình- Tuyên bố vòng lặp Từ chương này, bạn sẽ tiếp xúc với một điểm kiến thức quan trọng và mạnh mẽ - Câu lệnh vòng lặp. Trước khi đọc chương này, nếu bạn muốn vẽ 10.000 vòng tròn trong chương trình, bạn chỉ có thể thực hiện với một