Mục lục:

- Tác giả John Day day@howwhatproduce.com.

- Public 2024-01-30 13:30.

- Sửa đổi lần cuối 2025-06-01 06:10.

Để hoàn thành tài liệu hướng dẫn này, những thứ cần thiết duy nhất là máy tính, truy cập internet và một số phần mềm mô phỏng. Với mục đích của thiết kế này, tất cả các mạch và mô phỏng sẽ được chạy trên LTspice XVII. Phần mềm mô phỏng này chứa thư viện của hơn 1 000 thành phần giúp tạo mạch rất dễ dàng. Vì các mạch này sẽ được tổng quát hóa nên “UniversalOpAmp2” sẽ được sử dụng cho mọi trường hợp cần op-amp. Ngoài ra, mỗi op-amp được cung cấp bởi nguồn điện + 15V và -15V. Những bộ nguồn này không chỉ cung cấp năng lượng cho op-amp mà còn cắt điện áp đầu ra nếu nó đạt đến một trong hai điểm cực trị đó.

Bước 1: Thiết kế Bộ khuếch đại Dụng cụ

Sau khi tín hiệu đã được thu nhận, nó cần được khuếch đại để thực hiện các phép tính và lọc trên đó. Đối với điện tâm đồ, phương pháp khuếch đại phổ biến nhất là bộ khuếch đại thiết bị đo. Như đã nói ở trên, bộ khuếch đại thiết bị đo có nhiều lợi thế khi nói đến mạch khuếch đại, lớn nhất là trở kháng cao giữa các điện áp đầu vào. Để xây dựng mạch này, 3 op-amps đã được sử dụng kết hợp với bảy điện trở, với sáu trong số các điện trở có độ lớn tương đương. Mức tăng của hầu hết các điện tâm đồ là khoảng 1000 lần tín hiệu đầu vào [1]. Phương trình độ lợi của bộ khuếch đại thiết bị đo đạc như sau: Độ lợi = 1 + (2 * R1 / R2) * (R7 / R6). Để đơn giản, mọi điện trở được giả định là 1000 ôm, ngoại trừ R2, được xác định là 2 ôm. Các giá trị này cho độ lợi lớn hơn 1001 lần so với điện áp đầu vào. Độ lợi này đủ để khuếch đại các tín hiệu thu được để phân tích thêm. Tuy nhiên, bằng cách sử dụng phương trình, độ lợi có thể là bất cứ điều gì người ta muốn cho thiết kế mạch của họ.

Bước 2: Thiết kế bộ lọc băng thông

Bộ lọc thông dải là bộ lọc thông cao và bộ lọc thông thấp hoạt động phối hợp thường với một op-amp để cung cấp những gì được gọi là băng thông. Băng thông là một dải tần số có thể vượt qua trong khi tất cả các tần số khác, trên và dưới, đều bị từ chối. Tiêu chuẩn công nghiệp quy định rằng một điện tâm đồ tiêu chuẩn phải có băng thông từ 0,5 Hz đến 150 Hz [2]. Băng thông lớn này đảm bảo rằng tất cả các tín hiệu điện từ tim được ghi lại và không có tín hiệu nào trong số đó bị lọc ra. Tương tự như vậy, băng thông này từ chối bất kỳ độ lệch DC nào có thể gây nhiễu tín hiệu. Để thiết kế điều này, các điện trở và tụ điện cụ thể phải được chọn sao cho tần số cắt thông cao là 0,5 Hz và tần số cắt thông thấp là 150 Hz. Phương trình tần số cắt cho cả bộ lọc thông cao và thông thấp như sau: Fc = 1 / (2 * pi * RC). Đối với tính toán của tôi, một điện trở tùy ý đã được chọn, sau đó sử dụng Công thức 4, giá trị tụ điện được tính toán. Do đó, bộ lọc thông cao sẽ có giá trị điện trở 100, 000 ohms và giá trị tụ điện là 3,1831 microfarads. Tương tự như vậy, bộ lọc thông thấp sẽ có giá trị điện trở là 100, 000 ohms và giá trị tụ điện là 10,61 nano-farads. Biểu đồ của bộ lọc thông dải với các giá trị đã điều chỉnh được hiển thị.

Bước 3: Thiết kế bộ lọc Notch

Bộ lọc khía về cơ bản ngược lại với bộ lọc thông dải. Thay vì có một đường chuyền cao theo sau là một đường chuyền thấp, nó là một đường chuyền thấp theo sau một đường chuyền cao, do đó về cơ bản người ta có thể loại bỏ một dải nhiễu nhỏ. Đối với bộ lọc khía của điện tâm đồ, thiết kế bộ lọc có khía Twin-T đã được sử dụng. Thiết kế này cho phép lọc tần số trung tâm và cung cấp hệ số chất lượng lớn. Trong trường hợp này, tần số trung tâm để loại bỏ là 60 Hz. Sử dụng phương trình 4, các giá trị điện trở được tính toán bằng cách sử dụng giá trị tụ điện cho trước là 0,1 microfarads. Các giá trị điện trở được tính toán cho dải dừng 60 Hz là 26, 525 ohms. Khi đó R5 được tính là ½ của R3 và R4. C3 cũng được tính gấp đôi giá trị được chọn cho C1 và C2 [3]. Các điện trở tùy ý được chọn cho R1 và R2.

Bước 4: Mạch kết hợp

Sử dụng lưới, các thành phần này được đặt nối tiếp với nhau và hình ảnh của mạch điện đã hoàn thành. Theo một bài báo được xuất bản bởi Springer Science, mức tăng có thể chấp nhận được của mạch ECG phải vào khoảng 70 dB khi toàn bộ mạch được thiết lập [4].

Bước 5: Kiểm tra toàn bộ mạch

Khi tất cả các thành phần được đặt trong một loạt, cần phải xác nhận thiết kế. Thử nghiệm mạch này, cả quét tạm thời và xoay chiều đều được tiến hành để xác định xem tất cả các thành phần có hoạt động đồng thời hay không. Nếu đúng như vậy, điện áp đầu ra tạm thời vẫn sẽ bằng khoảng 1000 lần điện áp đầu vào. Tương tự như vậy, khi tiến hành quét AC, đồ thị bode bộ lọc thông dải sẽ được mong đợi với một rãnh ở tần số 60 Hz. Nhìn vào các hình ảnh trong hình, mạch này đã có thể thực hiện thành công cả hai mục tiêu đó. Một thử nghiệm khác là để xem hiệu quả của bộ lọc khía. Để kiểm tra điều này, một tín hiệu 60 Hz đã được đưa qua mạch. Như trong hình, độ lớn của đầu ra này chỉ lớn hơn đầu vào khoảng 5x, so với 1000x khi tần số nằm trong băng thông.

Bước 6: Nguồn lực:

[1] “Hệ thống đo ECG,” Columbia.edu, 2020. https://www.cisl.columbia.edu/kinget_group/student_projects/ECG%20Report/E6001%20ECG%20final%20report.htm (truy cập ngày 01 tháng 12, Năm 2020).

[2] L. G. Tereshchenko và M. E. Josephson, “Nội dung tần số và đặc điểm của dẫn truyền tâm thất,” Tạp chí điện tâm đồ, tập. 48, không. 6, trang 933-937, 2015, doi: 10.1016 / j.jelectrocard.2015.08.034.

[3] “Bộ lọc Dừng dải được gọi là Bộ lọc Từ chối”, Hướng dẫn Điện tử Cơ bản, ngày 22 tháng 5 năm 2018.

[4] N. Guler và U. Fidan, “Truyền tín hiệu điện tâm đồ không dây,” Springer Science, tập. Ngày 30 tháng 4 năm 2005, doi: 10.1007 / s10916-005-7980-5.

Đề xuất:

Điện tâm đồ tự động: Mô phỏng bộ lọc và khuếch đại bằng LTspice: 5 bước

Điện tâm đồ tự động: Mô phỏng bộ lọc và khuếch đại bằng LTspice: Đây là hình ảnh của thiết bị cuối cùng mà bạn sẽ xây dựng và thảo luận rất sâu về từng phần. Đồng thời mô tả các tính toán cho từng giai đoạn. Hình ảnh hiển thị sơ đồ khối cho thiết bị này

Bộ lọc thông thấp thụ động cho mạch âm thanh (Bộ lọc RC dạng tự do): 6 bước

Bộ lọc thông thấp thụ động cho mạch âm thanh (Bộ lọc RC dạng tự do): Một điều luôn khiến tôi gặp khó khăn khi chế tạo các nhạc cụ điện tử tùy chỉnh là nhiễu tiếng ồn liên tục trên tín hiệu âm thanh của tôi. Tôi đã thử các thủ thuật che chắn và các thủ thuật khác nhau để nối dây tín hiệu nhưng giải pháp đơn giản nhất sau khi xây dựng dường như b

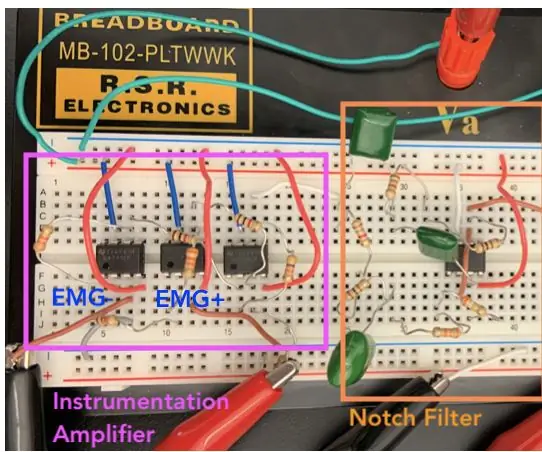

Điện tâm đồ tự động dễ dàng (1 Bộ khuếch đại, 2 Bộ lọc): 7 bước

Điện tâm đồ tự động dễ dàng (1 Bộ khuếch đại, 2 Bộ lọc): Điện tâm đồ (ECG) đo và hiển thị hoạt động điện của tim bằng cách sử dụng các điện cực khác nhau đặt trên da. Có thể tạo ECG bằng bộ khuếch đại thiết bị đo, bộ lọc rãnh và bộ lọc thông thấp. Cuối cùng, bộ lọc

Làm thế nào để biến một bộ khuếch đại ống guitar thành một đơn vị tiền khuếch đại / biến dạng (với hộp tải): 6 bước

Làm thế nào để biến một Amply Guitar Tube thành một Preamp / Thiết bị biến dạng (với Hộp tải): Xin chào tất cả các bạn !!! Đây là Tài liệu hướng dẫn đầu tiên của tôi, tôi sẽ giải thích cho bạn cách biến một chiếc Tube guitar amp nhỏ thành một bộ tiền khuếch đại / bàn đạp, với hộp tải; Tôi là người Pháp và tiếng Anh của tôi hạn chế, vì vậy nếu tôi có một số sai sót, xin vui lòng bỏ qua cho tôi !! :) TÔI KHÔNG KHUYẾN CÁO

LP-2010 AES17 1998 Bộ lọc Bộ khuếch đại chuyển mạch Low Pass (thông thấp): 4 bước

LP-2010 AES17 1998 Bộ lọc chuyển mạch Bộ khuếch đại thông thấp (thông thấp): Đây là một bộ khuếch đại hạng D tuyệt vời của bộ lọc thông thấp. hiệu suất chi phí cao